#### Microarchitectural Attacks:

#### From the Basics to Arbitrary Read and Write Primitives without any Software Bugs

#### **Daniel Gruss**

June 19, 2018

Graz University of Technology

Daniel Gruss — Graz University of Technology

Daniel Gruss — Graz University of Technology

#### 1337 4242

#### **FOOD CACHE**

#### Revolutionary concept!

Store your food at home, never go to the grocery store during cooking.

Can store **ALL** kinds of food.

ONLY TODAY INSTEAD OF \$1,300

ORDER VIA PHONE: +555 12345

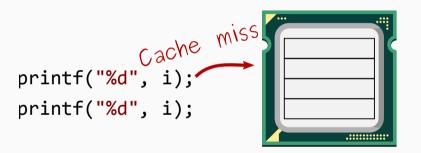

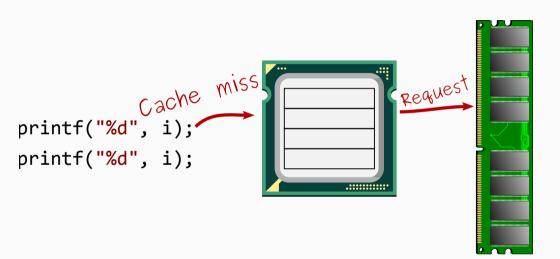

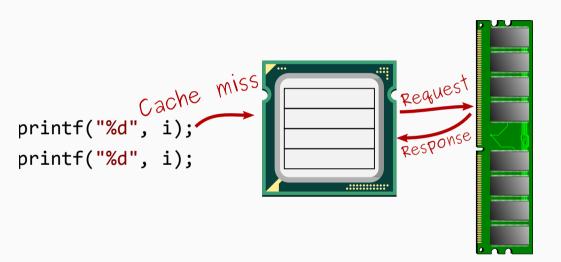

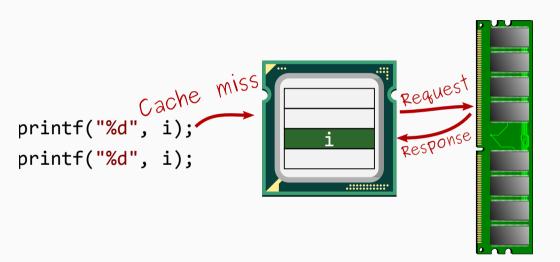

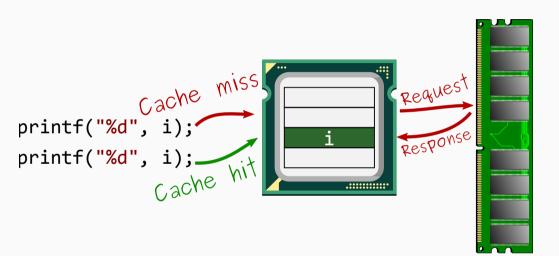

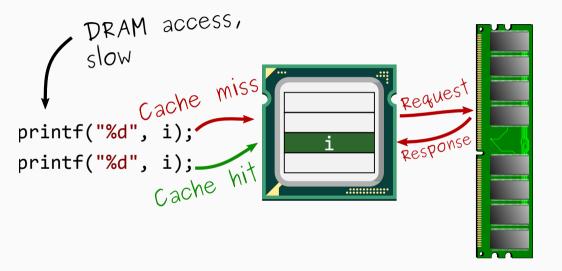

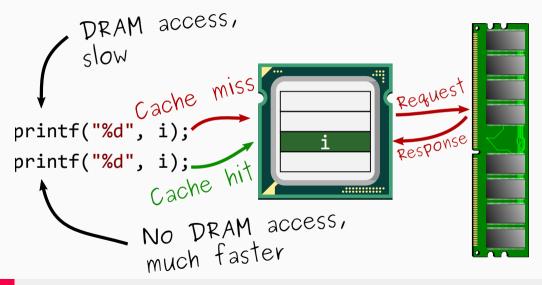

## printf("%d", i); printf("%d", i);

**CPU** Cache

**CPU** Cache

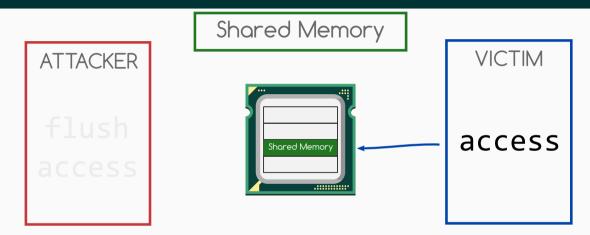

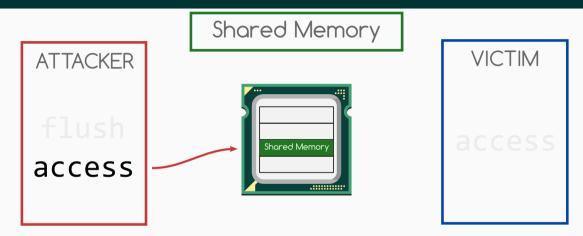

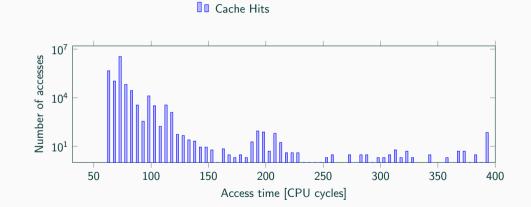

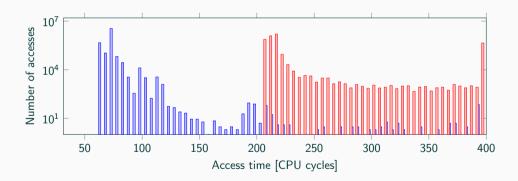

#### Cache Hits Cache Misses

|                                                                                                                          | Terminal |                   | - • •   | < Open | + | Untitled     | Document 1          | Save     | H | + × |

|--------------------------------------------------------------------------------------------------------------------------|----------|-------------------|---------|--------|---|--------------|---------------------|----------|---|-----|

| File Edit View Search Terminal Help                                                                                      |          |                   |         |        |   |              |                     |          |   |     |

| % sleep 2; ./spy 300 7f05140a4000-7f051417b000 r-xp 0x20000 00:02 26<br>8050 /usr/lib/x86_64-linux-gnu/gedit/libgedit.so |          |                   |         |        |   |              |                     |          |   |     |

| -                                                                                                                        |          |                   |         |        |   | I            |                     |          |   |     |

| 🚍 n naonaar                                                                                                              |          |                   | 7.7M 71 |        |   |              |                     |          |   |     |

| Threfetch1                                                                                                               |          | -NIR-14 03 2017 2 | - 🛛 🗎   |        |   |              |                     |          |   |     |

| File Edit View Search Terminal Help<br>shark% ./spy []                                                                   |          |                   |         |        |   |              |                     |          |   |     |

| phome-camer.ja.                                                                                                          |          |                   |         |        |   | Plain Text 👻 | Tab Width: 2 👻 🛛 Ln | 1, Col 1 | ŝ | 1NS |

Cache Template Attack Demo

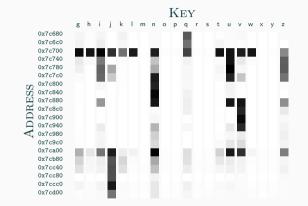

#### **Cache Template**

Daniel Gruss — Graz University of Technology

7

7. Serve with cooked and peeled potatoes

## Wait for an hour

## Wait for an hour

# LATENCY

1. Wash and cut vegetables

2. Pick the basil leaves and set aside

3. Heat 2 tablespoons of oil in a pan

4. Fry vegetables until golden and softened

1. Wash and cut vegetables

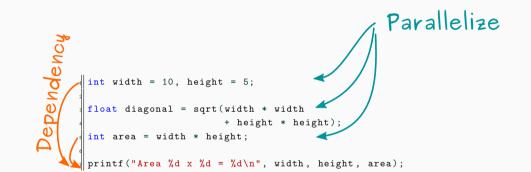

### Parallelize

2. Pick the basil leaves and set aside

3. Heat 2 tablespoons of oil in a pan

4. Fry vegetables until golden and softened

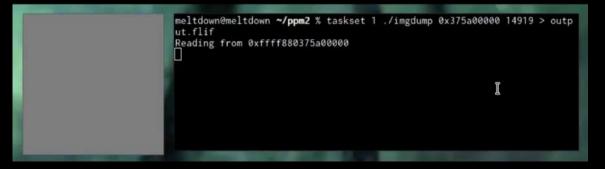

segfault at ffffffff81a000e0 ip 000000000400535

sp 00007ffce4a80610 error 5 in reader

segfault at ffffffff81a000e0 ip 000000000400535 sp 00007ffce4a80610 error 5 in reader

• Kernel addresses are not accessible

segfault at ffffffff81a000e0 ip 000000000400535 sp 00007ffce4a80610 error 5 in reader

- Kernel addresses are not accessible

- Are privilege checks also done when executing instructions out of order?

• Adapted code

```

*(volatile char*)0;

array[84 * 4096] = 0; // unreachable

```

• Adapted code

```

*(volatile char*)0;

array[84 * 4096] = 0; // unreachable

```

• Static code analyzer is not happy

1 warning: Dereference of null pointer

2 \*(volatile char\*)0;

• "Unreachable" code line was actually executed

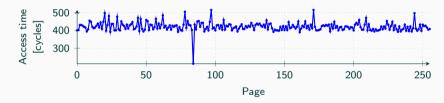

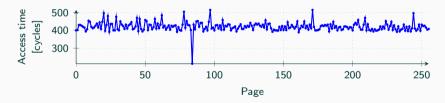

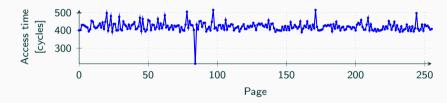

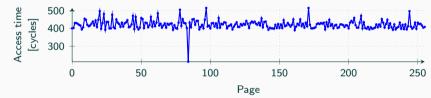

• Flush+Reload over all pages of the array

- "Unreachable" code line was actually executed

- Exception was only thrown afterwards

• Combine the two things

• Combine the two things

• Then check whether any part of array is cached

$\bullet~\mbox{Flush+Reload}$  over all pages of the array

• Index of cache hit reveals data

• Flush+Reload over all pages of the array

- Index of cache hit reveals data

- Permission check is in some cases not fast enough

| pwd                     | ×     |

|-------------------------|-------|

| Unlock Password Manager |       |

| U                       | nlock |

|      |       |       |         |          | Terminal | × |

|------|-------|-------|---------|----------|----------|---|

| File | Edit  | View  | Search  | Terminal | Help     |   |

| nsch | warz@ | lab06 | :~/Docu | uments\$ |          |   |

|      |       |       |         |          |          |   |

|      |       |       |         |          |          |   |

|      |       |       |         |          |          |   |

|      |       |       |         |          |          |   |

|      |       |       |         |          |          |   |

| 2        |         |           |               |          |           | Documents : zsł   | n — Konsole <2 | >                    |                   | * ~ ^ §   |

|----------|---------|-----------|---------------|----------|-----------|-------------------|----------------|----------------------|-------------------|-----------|

| File     | Edit    | View      | Bookmarks     | Settings | Help      |                   |                |                      |                   |           |

| 01 < Nos | clehp - | /Documen  | its % taskset |          |           | c200000 40016 > / | out.pps] A     | #lcnael@hp ∽/Documen | ts % fehreload Ø, | 1 out.ppa |

|          | Docu    | ments : z | sh 💽          | Documen  | nts : zsh |                   |                | Documents : zsh      | Documents : zsh   |           |

## CAN YOU ENHANCE THAT

|                                                  |                   |     | f94b76a0: e5                                                                                    |

|--------------------------------------------------|-------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------|

|                                                  |                   |     | f94b76b0: 70 52 b8 6b 96 7f XX  pR.k                                                                     |

|                                                  |                   |     | 194b76c0: 09 XX                                                                                 |

|                                                  |                   |     | f94b76d0: XX                                                                                    |

|                                                  |                   | _   | f94b76f0: 12 XX e0 81 19 XX e0 81 44 6f 6c 70 68 69 6e 31                                                                           |

| Saved Logins                                     |                   | - H | f94b7700: 38 e5                                                                                 |

|                                                  |                   | _   | f94b7710: 70 52 b8 6b 96 7f XX  pR.k                                                                     |

| Search                                           |                   | 9   | f94b7720: XX                                                                                    |

|                                                  |                   |     | 194b7730: XX XX XX XX 4a XX IJ                                                                     |

| ogins for the following sites are stored on your | computer:         |     | f94b7740: XX                                                                                    |

|                                                  |                   |     | 19467750: XX 40 81 69 6e 73 74 [<br>19467760: 61 5f 30 32 30 33 e5 [a_0203 |

| Site • Username Passv                            | rord Last Changed | 15  | 1945770: 70 52 18 7d 28 7f XX XX XX XX XX XX XX XX XX (pR.)(                                                                        |

| https://accounts.gomeitdown@ligmail.com_secretp  | vol 28 Dez 2017   |     | 194b7780: XX                                                                                    |

| https://signin.ebay meltdowng0gmail.com Dolphin  | 18 28 Dez. 2017   | - 1 | f94b7790: XX XX XX XX 54 XX                                                                     |

|                                                  | 00 Pu- 0017       |     | f94b77b0: XX 73 65 63 72                                                                           |

| https://www.amaz meltdown@bgmail.com hunter2     | 28. Dez. 2017     |     | f94b77c0: 65 74 70 77 64 30 e5                                                                  |

| https://www.facebmeltdown@facebook fb1234/       | 28. Dez. 2017     |     | f94b77d0: 30 b4 18 7d 28 7f XX (0)(                                                                      |

| https://www.instagmeltdown@gmail.com_insta_02    | 03 28. Dez. 2017  |     | f94b77e0: XX                                                                                    |

| a international menoralization and and           | 03 20.002.2017    |     | 1946//10: AA                                                                                    |

|                                                  |                   |     | f94b7810: 68 74 74 70 73 3a 2f 2f 61 64 64 6f 6e 73 2e 63 https://d                                                                 |

|                                                  |                   | -   | f94b7820: 64 6e 2e 6d 6f 7a 69 6c 6c 61 2e 6e 65 74 2f 75  dn.mozill                                                                |

| Remove Remove All                                | Hide Password     | is  | f94b7830: 73 65 72 2d 6d 65 64 69 61 2f 61 64 64 6f 6e 5f  ser-media                                                                |

|                                                  |                   | -   | f94b7840: 69 63 6f 6e 73 2f 33 35 34 2f 33 35 34 33 39 39  icons/354                                                                |

|                                                  | Close             |     | f94b7850: 2d 36 34 2e 70 6e 67 3f 6d 6f 64 69 66 69 65 64  -64.png?m                                                                |

|                                                  |                   | - 1 | f94b7860: 3d 31 34 35 32 32 34 34 38 31 35 XX XX XX XX  =14522448                                                                   |

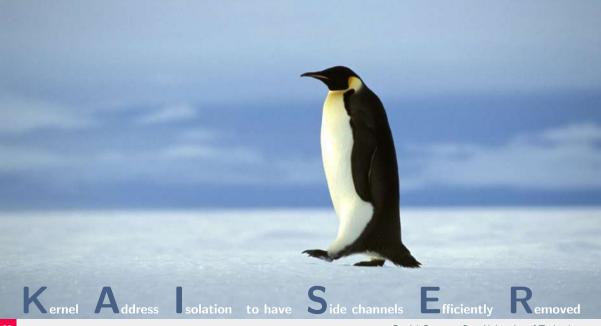

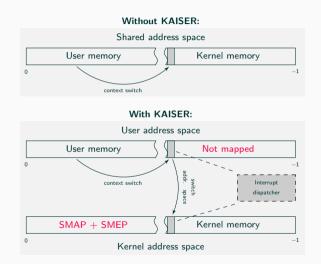

## How to mitigate Meltdown?

• Kernel addresses in user space are a problem

- Kernel addresses in user space are a problem

- Why don't we take the kernel addresses...

### • ...and remove them if not needed?

- ...and remove them if not needed?

- User accessible check in hardware is not reliable

# **CAN'T LEAK DATA**

# IF THERE IS NO DATA

**KAISER** /'kAIzə/ 1. [german] Emperor, ruler of an empire 2. largest penguin, emperor penguin

Removed

Address Isolation to have Side channels Efficiently

• We published KAISER in July 2017

- We published KAISER in July 2017

- Intel and others improved and merged it into Linux as KPTI (Kernel Page Table Isolation)

- We published KAISER in July 2017

- Intel and others improved and merged it into Linux as KPTI (Kernel Page Table Isolation)

- Microsoft implemented similar concept in Windows 10

- We published KAISER in July 2017

- Intel and others improved and merged it into Linux as KPTI (Kernel Page Table Isolation)

- Microsoft implemented similar concept in Windows 10

- Apple implemented it in macOS 10.13.2 and called it "Double Map"

- We published KAISER in July 2017

- Intel and others improved and merged it into Linux as KPTI (Kernel Page Table Isolation)

- Microsoft implemented similar concept in Windows 10

- Apple implemented it in macOS 10.13.2 and called it "Double Map"

- All share the same idea: switching address spaces on context switch

### Meltdown and Spectre

### **Meltdown and Spectre**

## **SPECTRE**

## **Prosciutto**

# Funghi

## **Speculative Cooking**

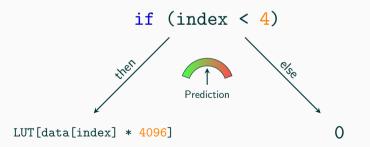

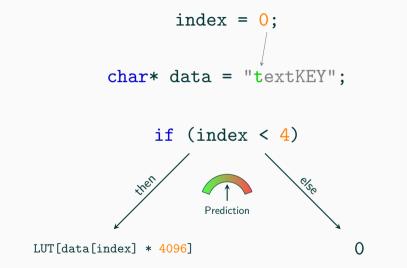

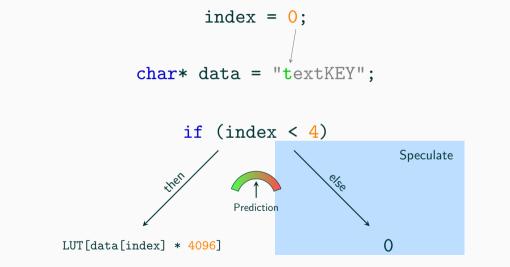

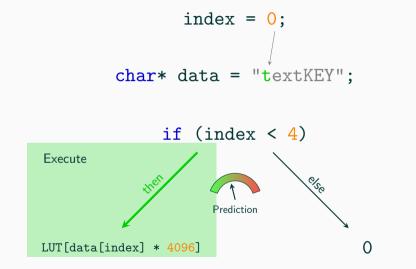

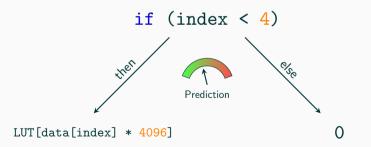

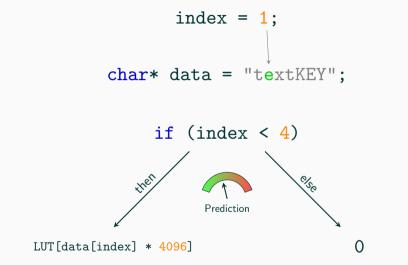

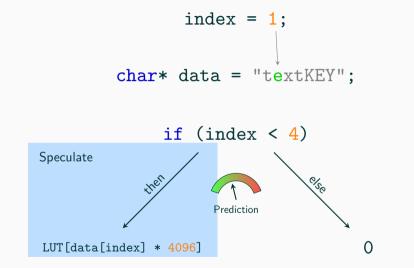

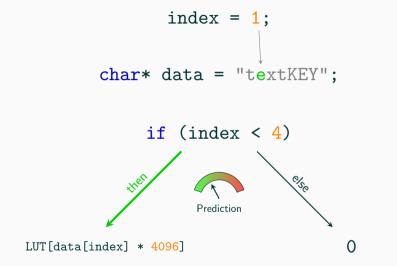

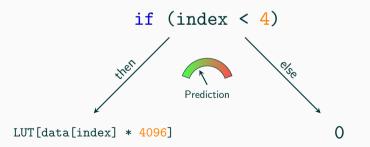

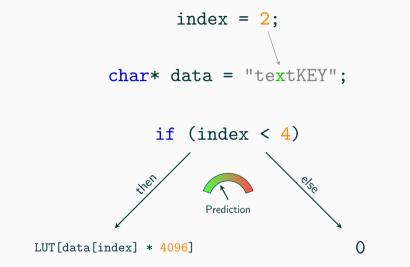

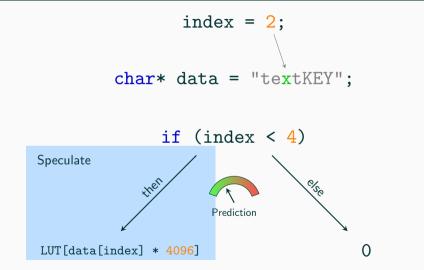

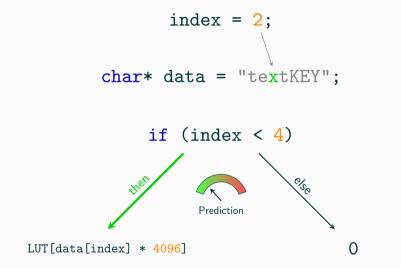

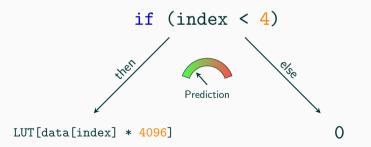

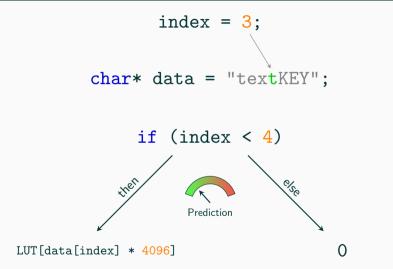

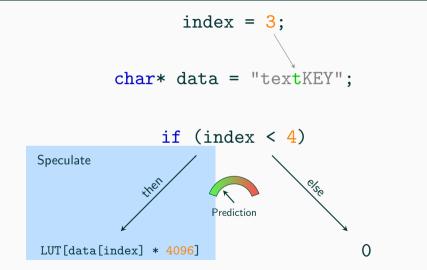

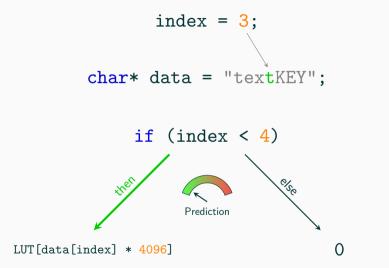

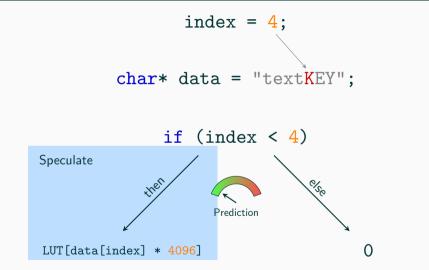

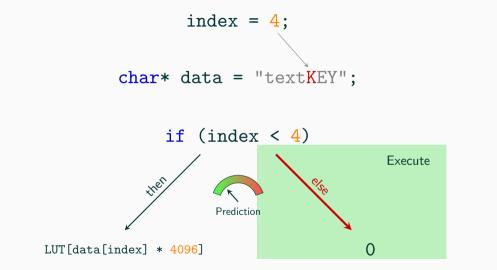

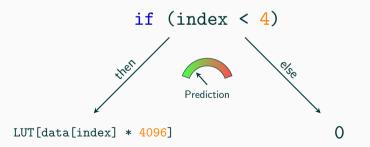

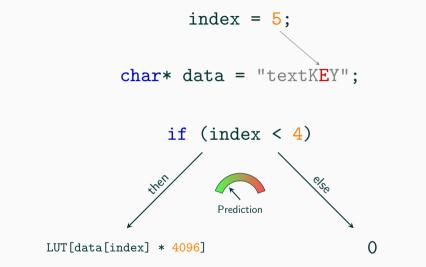

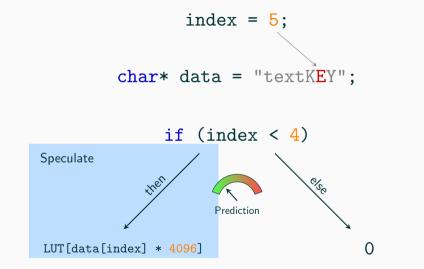

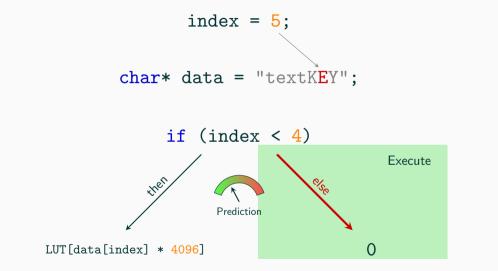

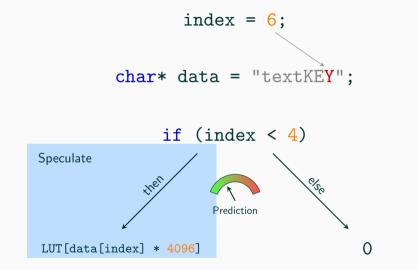

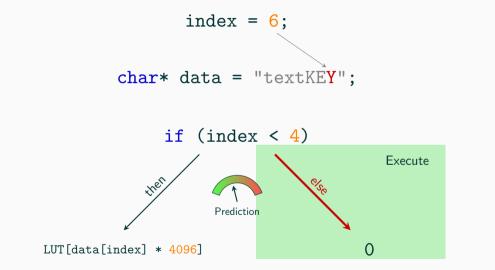

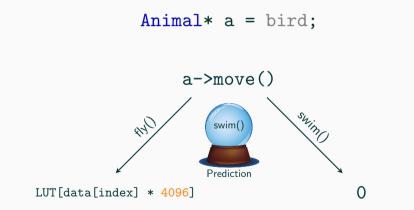

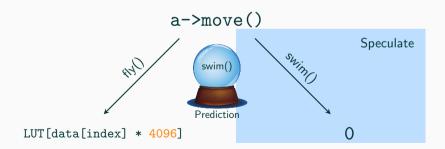

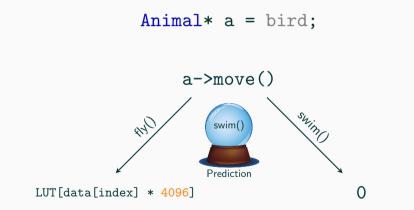

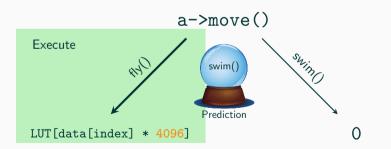

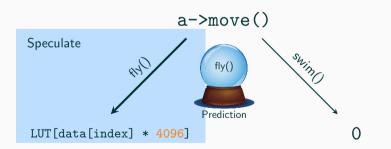

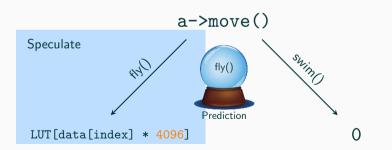

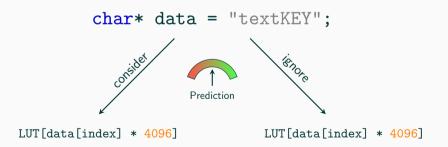

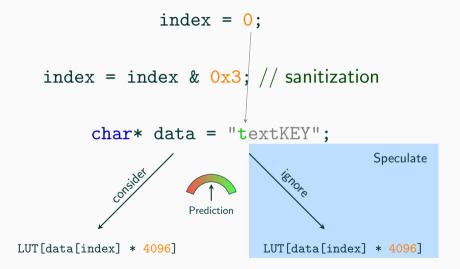

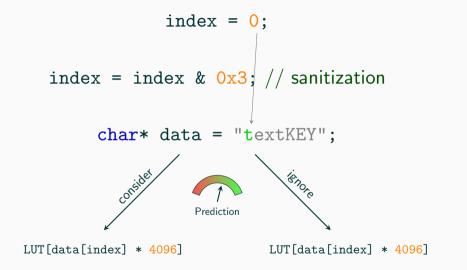

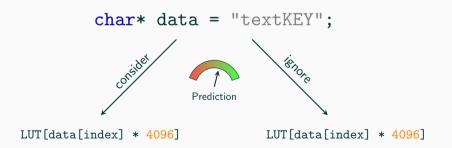

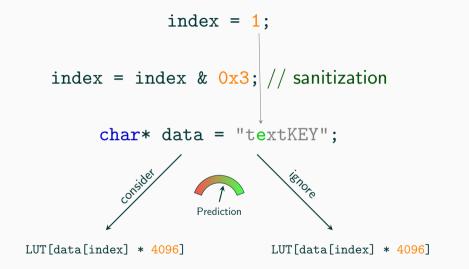

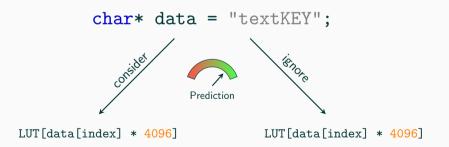

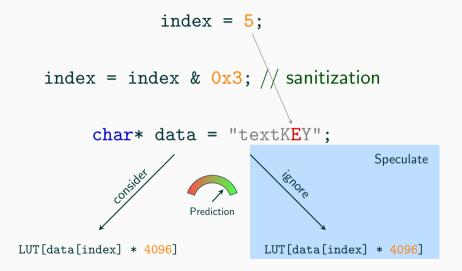

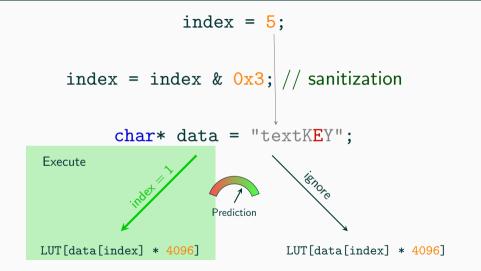

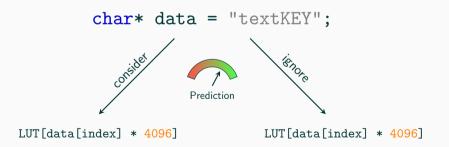

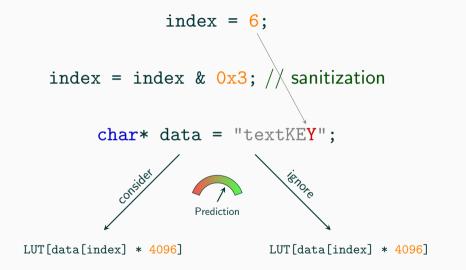

• Mistrains branch prediction

- Mistrains branch prediction

- CPU speculatively executes code which should not be executed

- Mistrains branch prediction

- CPU speculatively executes code which should not be executed

- Can also mistrain indirect calls

- Mistrains branch prediction

- CPU speculatively executes code which should not be executed

- Can also mistrain indirect calls

- $\rightarrow\,$  Spectre "convinces" program to execute code

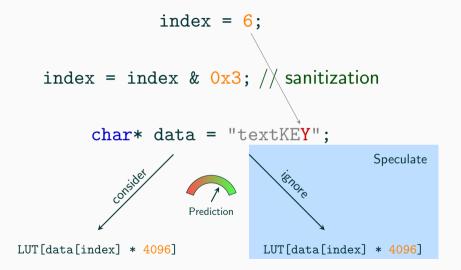

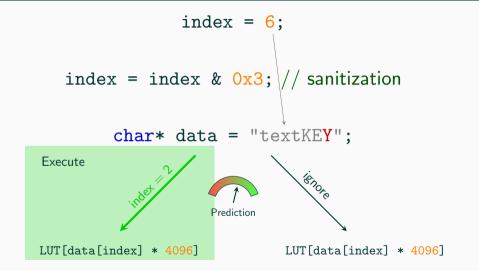

index =

$$0;$$

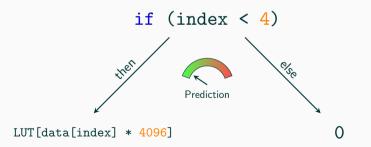

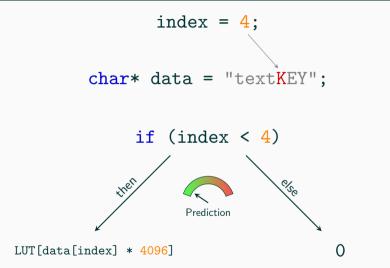

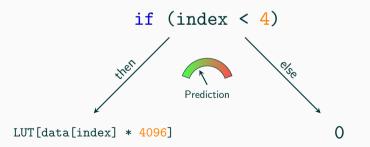

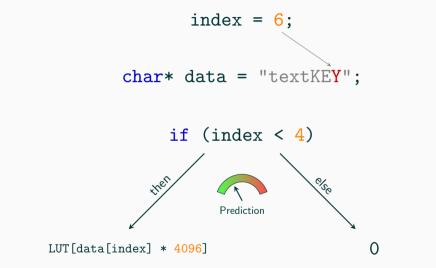

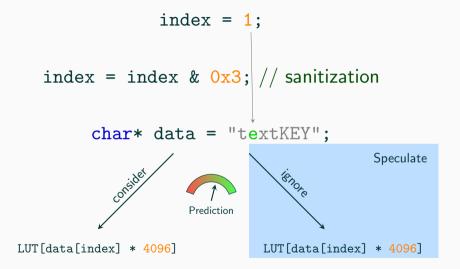

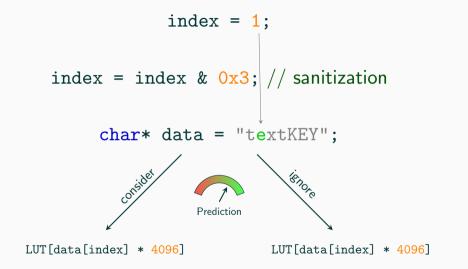

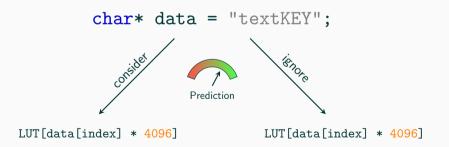

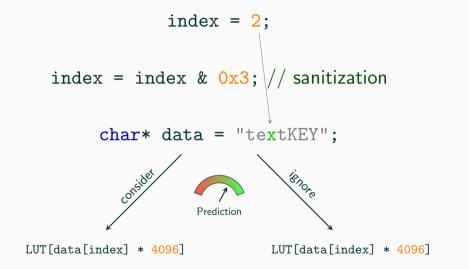

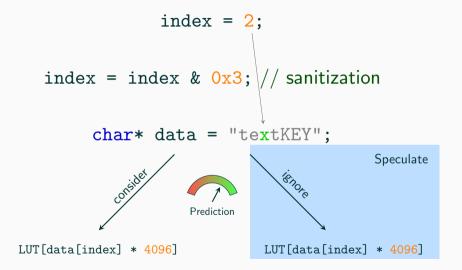

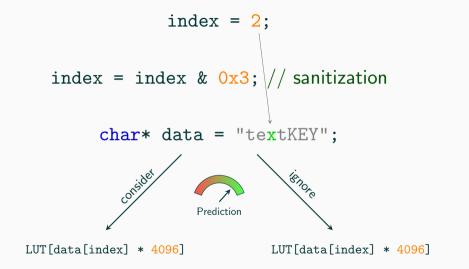

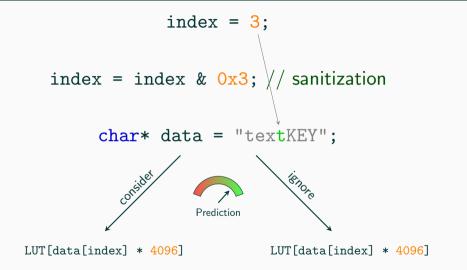

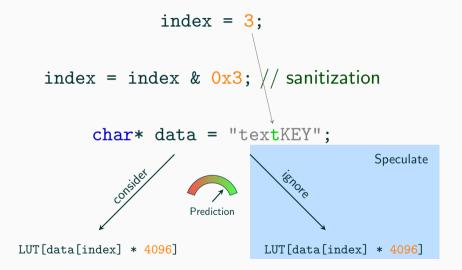

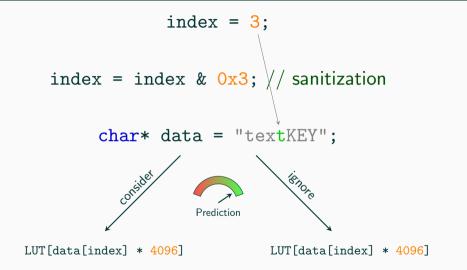

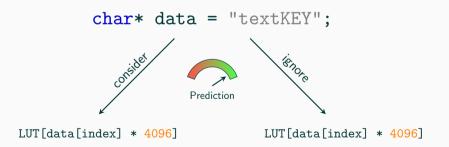

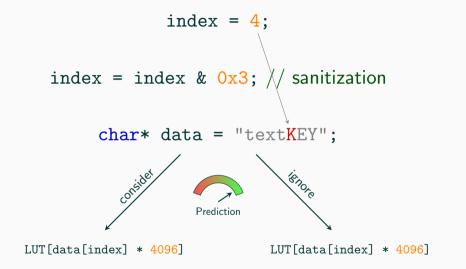

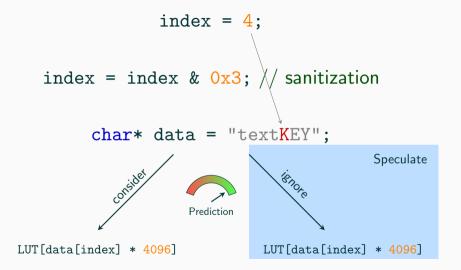

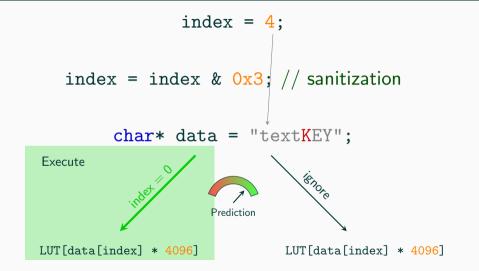

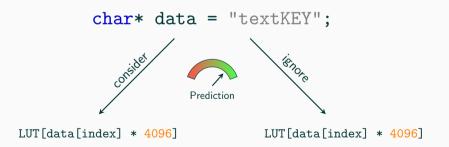

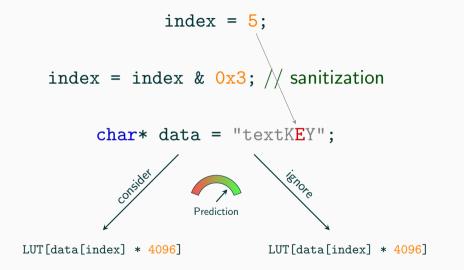

#### Spectre (variant 1)

25

index =

$$1;$$

Daniel Gruss — Graz University of Technology

25

index =

$$2;$$

index =

$$3;$$

index =

$$4;$$

index =

$$5;$$

www.tugraz.at 📕

## Spectre (variant 1)

25

www.tugraz.at 📕

www.tugraz.at 📕

index =

$$6;$$

www.tugraz.at 📕

Spectre (variant 1)

www.tugraz.at 📕

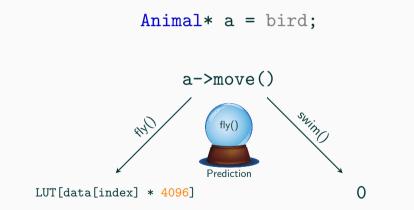

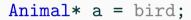

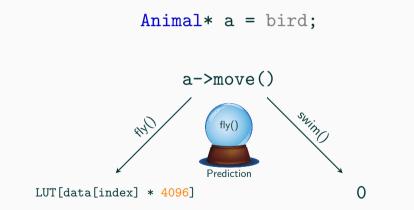

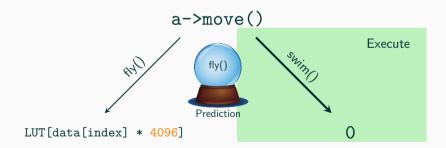

## Animal\* a = bird;

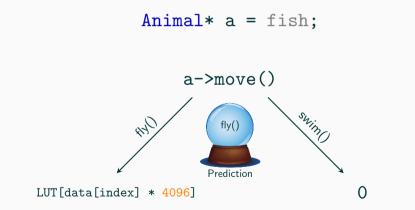

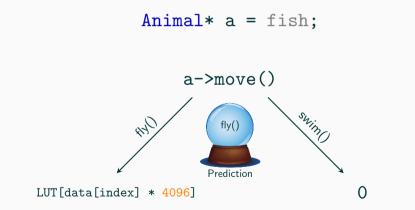

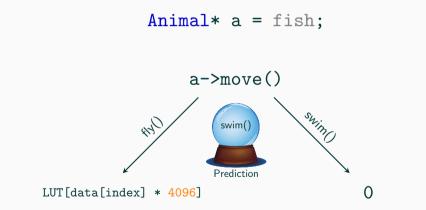

## Animal\* a = fish;

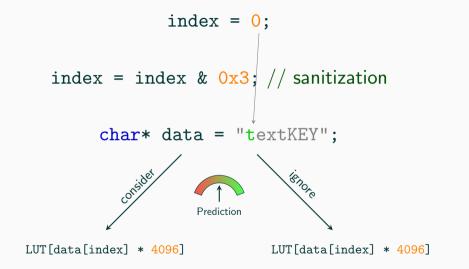

index =

$$0;$$

index = index &

$$0x3$$

; // sanitization

index = 1;

index = index & 0x3; // sanitization

index =

$$2;$$

index = index &

$$0x3$$

; // sanitization

index =

$$3;$$

index = index &

$$0x3$$

; // sanitization

index =

$$4;$$

index = index &

$$0x3$$

; // sanitization

index =

$$5;$$

index = index &

$$0x3$$

; // sanitization

www.tugraz.at

index =

$$6;$$

index = index &

$$0x3$$

; // sanitization

• Trivial approach: disable speculative execution

- Trivial approach: disable speculative execution

- No wrong speculation if there is no speculation

- Trivial approach: disable speculative execution

- No wrong speculation if there is no speculation

- Problem: massive performance hit!

- Trivial approach: disable speculative execution

- No wrong speculation if there is no speculation

- Problem: massive performance hit!

- Also: How to disable it?

- Trivial approach: disable speculative execution

- No wrong speculation if there is no speculation

- Problem: massive performance hit!

- Also: How to disable it?

- Speculative execution is deeply integrated into CPU

• Workaround: insert instructions stopping speculation

- Workaround: insert instructions stopping speculation

- $\rightarrow\,$  insert after every bounds check

- Workaround: insert instructions stopping speculation

- $\rightarrow\,$  insert after every bounds check

- ×86: LFENCE, ARM: CSDB

- Workaround: insert instructions stopping speculation

- $\rightarrow\,$  insert after every bounds check

- ×86: LFENCE, ARM: CSDB

- Available on all Intel CPUs, retrofitted to existing ARMv7 and ARMv8

• Speculation barrier requires compiler supported

- Speculation barrier requires compiler supported

- Already implemented in GCC, LLVM, and MSVC

- Speculation barrier requires compiler supported

- Already implemented in GCC, LLVM, and MSVC

- Can be automated (MSVC)  $\rightarrow$  not really reliable

- Speculation barrier requires compiler supported

- Already implemented in GCC, LLVM, and MSVC

- Can be automated (MSVC)  $\rightarrow$  not really reliable

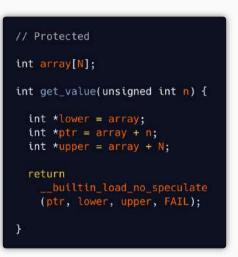

- Explicit use by programmer: \_\_builtin\_load\_no\_speculate

```

// Unprotected

int array[N];

int get_value(unsigned int n) {

int tmp;

if (n < N) {

tmp = array[n]

} else {

tmp = FAIL;

}

return tmp;

}

```

```

// Unprotected

int array[N];

int get_value(unsigned int n) {

int tmp;

if (n < N) {

tmp = array[n]

} else {

tmp = FAIL:

}

return tmp;

```

• Speculation barrier works if affected code constructs are known

- Speculation barrier works if affected code constructs are known

- Programmer has to fully understand vulnerability

- Speculation barrier works if affected code constructs are known

- Programmer has to fully understand vulnerability

- Automatic detection is not reliable

- Speculation barrier works if affected code constructs are known

- Programmer has to fully understand vulnerability

- Automatic detection is not reliable

- Non-negligible performance overhead of barriers

Intel released microcode updates

• Indirect Branch Restricted Speculation (IBRS):

୦-I-୦-I-୦ I-୦-I-୦-I ୦-I-୦-I-୦ I-୦-I-୦-I

- Indirect Branch Restricted Speculation (IBRS):

- Do not speculate based on anything before entering IBRS mode

୦-I-୦-I-୦ I-୦-I-୦-I ୦-I-୦-I-୦ I-୦-I-୦-I

Daniel Gruss — Graz University of Technology

- Indirect Branch Restricted Speculation (IBRS):

- Do not speculate based on anything before entering IBRS mode

- $\rightarrow\,$  lesser privileged code cannot influence predictions

୦-I-୦-I-୦ I-୦-I-୦-I ୦-I-୦-I-୦ I-୦-I-୦-I

- Indirect Branch Restricted Speculation (IBRS):

- Do not speculate based on anything before entering IBRS mode

- $\rightarrow\,$  lesser privileged code cannot influence predictions

- Indirect Branch Predictor Barrier (IBPB):

୦-I-୦-I-୦ I-୦-I-୦-I ୦-I-୦-I-୦ I-୦-I-୦-I

- Indirect Branch Restricted Speculation (IBRS):

- Do not speculate based on anything before entering IBRS mode

- $\rightarrow\,$  lesser privileged code cannot influence predictions

- Indirect Branch Predictor Barrier (IBPB):

- Flush branch-target buffer

୦ାଚାଚ ାଚାଚା ୦ାଚାଚ ାଚାଚା

- Indirect Branch Restricted Speculation (IBRS):

- Do not speculate based on anything before entering IBRS mode

- $\rightarrow\,$  lesser privileged code cannot influence predictions

- Indirect Branch Predictor Barrier (IBPB):

- Flush branch-target buffer

- Single Thread Indirect Branch Predictors (STIBP):

0-1-0-1-0 1-0-1-0-1 0-1-0-1-0 1-0-1-0-1

- Indirect Branch Restricted Speculation (IBRS):

- Do not speculate based on anything before entering IBRS mode

- $\rightarrow\,$  lesser privileged code cannot influence predictions

- Indirect Branch Predictor Barrier (IBPB):

- Flush branch-target buffer

- Single Thread Indirect Branch Predictors (STIBP):

- Isolates branch prediction state between two hyperthreads

Daniel Gruss — Graz University of Technology

0-1-0-1-0 1-0-1-0-1 0-1-0-1-0 1-0-1-0-1 Retpoline (compiler extension)

```

Retpoline (compiler extension)

```

```

push <call_target>

call 1f

2: ; speculation will continue here

lfence ; speculation barrier

jmp 2b ; endless loop

1:

lea 8(%rsp), %rsp ; restore stack pointer

ret ; the actual call to <call_target>

```

$\rightarrow\,$  always predict to enter an endless loop

```

Retpoline (compiler extension)

```

```

push <call_target>

call 1f

2: ; speculation will continue here

lfence ; speculation barrier

jmp 2b ; endless loop

1:

lea 8(%rsp), %rsp ; restore stack pointer

ret ; the actual call to <call_target>

```

- $\rightarrow\,$  always predict to enter an endless loop

- instead of the correct (or wrong) target function

```

Retpoline (compiler extension)

```

```

push <call_target>

call 1f

2: ; speculation will continue here

lfence ; speculation barrier

jmp 2b ; endless loop

1:

lea 8(%rsp), %rsp ; restore stack pointer

ret ; the actual call to <call_target>

```

- $\rightarrow\,$  always predict to enter an endless loop

- instead of the correct (or wrong) target function  $\rightarrow$  performance?

```

Retpoline (compiler extension)

```

```

push <call_target>

call 1f

2: ; speculation will continue here

lfence ; speculation barrier

jmp 2b ; endless loop

1:

lea 8(%rsp), %rsp ; restore stack pointer

ret ; the actual call to <call_target>

```

- $\rightarrow\,$  always predict to enter an endless loop

- instead of the correct (or wrong) target function  $\rightarrow$  performance?

- On Broadwell or newer:

```

Retpoline (compiler extension)

```

```

push <call_target>

call 1f

2: ; speculation will continue here

lfence ; speculation barrier

jmp 2b ; endless loop

1:

lea 8(%rsp), %rsp ; restore stack pointer

ret ; the actual call to <call_target>

```

- $\rightarrow\,$  always predict to enter an endless loop

- instead of the correct (or wrong) target function  $\rightarrow$  performance?

- On Broadwell or newer:

- ret may fall-back to the BTB for prediction

```

Retpoline (compiler extension)

```

```

push <call_target>

call 1f

2: ; speculation will continue here

lfence ; speculation barrier

jmp 2b ; endless loop

1:

lea 8(%rsp), %rsp ; restore stack pointer

ret ; the actual call to <call_target>

```

- $\rightarrow\,$  always predict to enter an endless loop

- instead of the correct (or wrong) target function  $\rightarrow$  performance?

- On Broadwell or newer:

- ret may fall-back to the BTB for prediction

- $\rightarrow\,$  microcode patches to prevent that

• ARM provides hardened Linux kernel

Daniel Gruss — Graz University of Technology

- ARM provides hardened Linux kernel

- Clears branch-predictor state on context switch

- ARM provides hardened Linux kernel

- Clears branch-predictor state on context switch

- Either via instruction (BPIALL)...

- ARM provides hardened Linux kernel

- Clears branch-predictor state on context switch

- Either via instruction (BPIALL)...

- ...or workaround (disable/enable MMU)

- ARM provides hardened Linux kernel

- Clears branch-predictor state on context switch

- Either via instruction (BPIALL)...

- ...or workaround (disable/enable MMU)

- Non-negligible performance overhead ( $\approx$  200-300 ns)

୦-I-୦-I-୦ I-୦-I-୦-I ୦-I-୦-I-୦ I-୦-I-୦-I

Intel released microcode updates

0-1-0-1-0 1-0-1-0-1 0-1-0-1-0 1-0-1-0-1

Intel released microcode updates

- Disable store-to-load-forward speculation

- Performance impact of 2-8%

• Prevent access to high-resolution timer

$\rightarrow~\mbox{Own}$  timer using timing thread

- Prevent access to high-resolution timer

- $\rightarrow~{\rm Own}$  timer using timing thread

- Flush instruction only privileged

- Prevent access to high-resolution timer

- $\rightarrow~{\rm Own}$  timer using timing thread

- Flush instruction only privileged

- $\rightarrow\,$  Cache eviction through memory accesses

- Prevent access to high-resolution timer

- $\rightarrow~{\rm Own}$  timer using timing thread

- Flush instruction only privileged

- $\rightarrow\,$  Cache eviction through memory accesses

- Just move secrets into secure world

- Prevent access to high-resolution timer

- $\rightarrow~{\rm Own}$  timer using timing thread

- Flush instruction only privileged

- $\rightarrow\,$  Cache eviction through memory accesses

- Just move secrets into secure world

- $\rightarrow\,$  Spectre works on secure enclaves

• Out-of-Order Execution

### Spectre

• Speculative Execution (subset of Out-of-Order Execution)

- Out-of-Order Execution

- has nothing to do with branch prediction

- Speculative Execution (subset of Out-of-Order Execution)

- fundamentally builds on branch (mis)prediction

- Out-of-Order Execution

- has nothing to do with branch prediction

- turning off speculative execution entirely has no effect on Meltdown

- Speculative Execution (subset of Out-of-Order Execution)

- fundamentally builds on branch (mis)prediction

- turning off speculative execution entirely would work

- Out-of-Order Execution

- has nothing to do with branch prediction

- turning off speculative execution entirely has no effect on Meltdown

- $\rightarrow$  melts down the isolation provided by the <code>user\_accessible-bit</code>

- Speculative Execution (subset of Out-of-Order Execution)

- fundamentally builds on branch (mis)prediction

- turning off speculative execution entirely would work

- has nothing to do with the user\_accessible-bit

- Out-of-Order Execution

- has nothing to do with branch prediction

- turning off speculative execution entirely has no effect on Meltdown

- → melts down the isolation provided by the user\_accessible-bit

- in theory: OoO not required, pipelining can be sufficient

- Speculative Execution (subset of Out-of-Order Execution)

- fundamentally builds on branch (mis)prediction

- turning off speculative execution entirely would work

- has nothing to do with the user\_accessible-bit

- KAISER has no effect on Spectre at all

- Out-of-Order Execution

- has nothing to do with branch prediction

- turning off speculative execution entirely has no effect on Meltdown

- → melts down the isolation provided by the user\_accessible-bit

- in theory: OoO not required, pipelining can be sufficient

- mitigated by KAISER

- Speculative Execution (subset of Out-of-Order Execution)

- fundamentally builds on branch (mis)prediction

- turning off speculative execution entirely would work

- has nothing to do with the user\_accessible-bit

- KAISER has no effect on Spectre at all

- performs illegal memory accesses  $\rightarrow$  we need to take care of processor exceptions

#### Spectre

• performs only legal memory accesses

- performs illegal memory accesses  $\rightarrow$  we need to take care of processor exceptions

- exception handling

- performs only legal memory accesses

- has nothing to do with exception handling

## Meltdown

- performs illegal memory accesses  $\rightarrow$  we need to take care of processor exceptions

- exception handling

- $\bullet\,$  exception suppression with TSX

# Spectre

- performs only legal memory accesses

- has nothing to do with exception handling or suppression

## Meltdown

- performs illegal memory accesses  $\rightarrow$  we need to take care of processor exceptions

- exception handling

- $\bullet\,$  exception suppression with TSX

- exception suppression with branch misprediction

## Spectre

- performs only legal memory accesses

- has nothing to do with exception handling or suppression

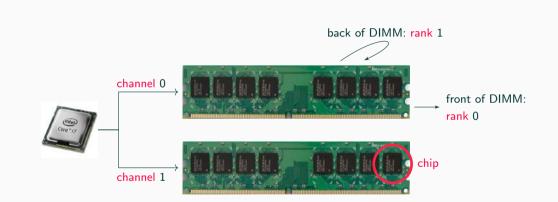

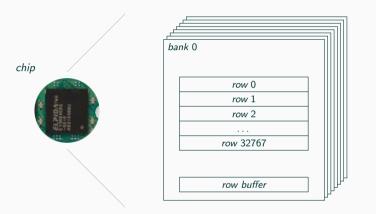

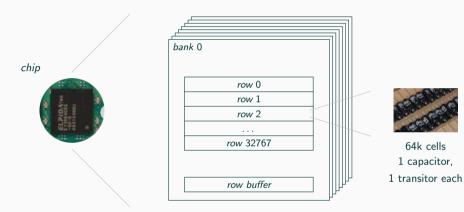

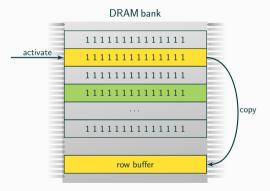

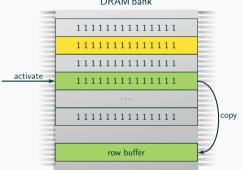

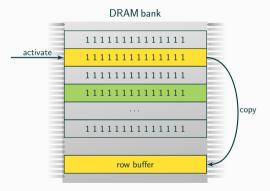

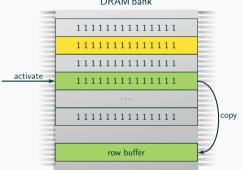

# What if we want to modify data?

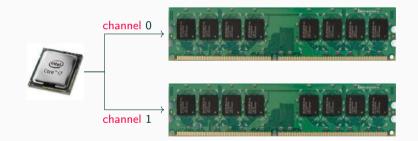

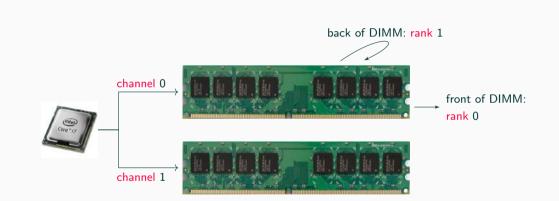

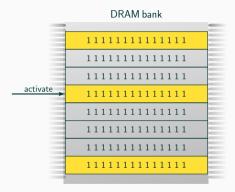

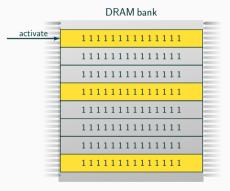

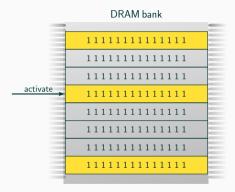

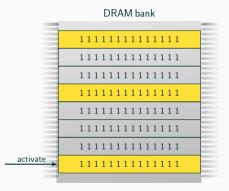

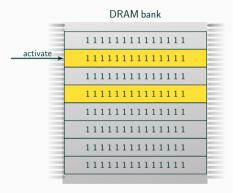

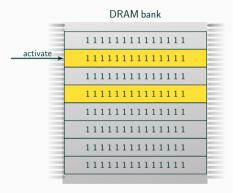

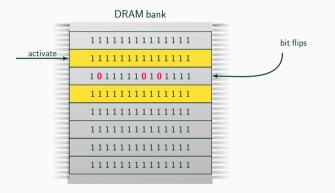

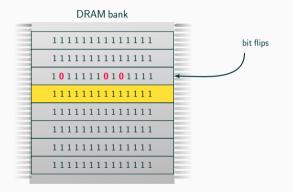

- Cells leak  $\rightarrow$  repetitive refresh necessary

- Maximum interval between refreshes to guarantee data integrity

- Cells leak faster upon proximate accesses  $\rightarrow$  Rowhammer

- Cells leak → repetitive refresh necessary

- Maximum interval between refreshes to guarantee data integrity

- Cells leak faster upon proximate accesses  $\rightarrow$  Rowhammer

- Cells leak  $\rightarrow$  repetitive refresh necessary

- Maximum interval between refreshes to guarantee data integrity

- Cells leak faster upon proximate  $accesses \rightarrow Rowhammer$

- Cells leak → repetitive refresh necessary

- Maximum interval between refreshes to guarantee data integrity

- Cells leak faster upon proximate accesses  $\rightarrow$  Rowhammer

- Cells leak  $\rightarrow$  repetitive refresh necessary

- Maximum interval between refreshes to guarantee data integrity

- Cells leak faster upon proximate  $accesses \rightarrow Rowhammer$

- Cells leak  $\rightarrow$  repetitive refresh necessary

- Maximum interval between refreshes to guarantee data integrity

- Cells leak faster upon proximate  $accesses \rightarrow Rowhammer$

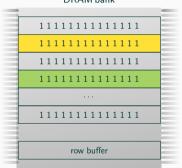

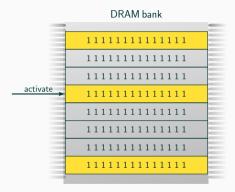

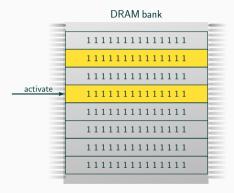

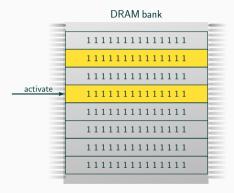

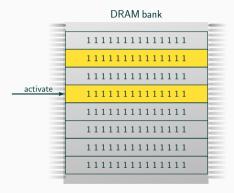

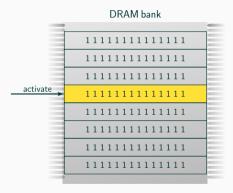

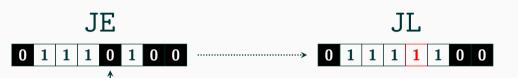

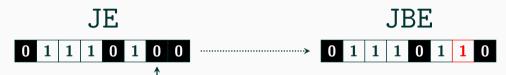

• There are two different hammering techniques

- There are two different hammering techniques

- #1: Hammer one row next to victim row and other random rows

- There are two different hammering techniques

- #1: Hammer one row next to victim row and other random rows

- #2: Hammer two rows neighboring victim row

- There are three different hammering techniques

- #1: Hammer one row next to victim row and other random rows

- #2: Hammer two rows neighboring victim row

- #3: Hammer only one row next to victim row

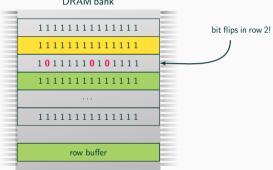

# DRAM bank \_

### Daniel Gruss — Graz University of Technology

# DRAM bank \_

### Daniel Gruss — Graz University of Technology

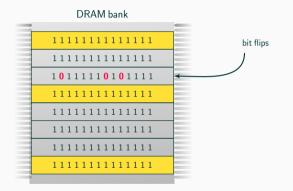

• They are not random  $\rightarrow$  highly reproducible flip pattern!

- They are not random  $\rightarrow$  highly reproducible flip pattern!

- 1. Choose a data structure that you can place at arbitrary memory locations

- They are not random  $\rightarrow$  highly reproducible flip pattern!

- 1. Choose a data structure that you can place at arbitrary memory locations

- 2. Scan for "good" flips

- They are not random  $\rightarrow$  highly reproducible flip pattern!

- 1. Choose a data structure that you can place at arbitrary memory locations

- 2. Scan for "good" flips

- 3. Place data structure there

- They are not random  $\rightarrow$  highly reproducible flip pattern!

- 1. Choose a data structure that you can place at arbitrary memory locations

- 2. Scan for "good" flips

- 3. Place data structure there

- 4. Trigger bit flip again

• Many applications perform actions as root

• Many applications perform actions as root

- Many applications perform actions as root

- They can be used by unprivileged users as well

- Many applications perform actions as root

- They can be used by unprivileged users as well

- Many applications perform actions as root

- They can be used by unprivileged users as well

- sudo

0 1

0 0

www.tugraz.at 📕

www.tugraz.at 📕

0 0

www.tugraz.at 📕

0 1

www.tugraz.at 📕

www.tugraz.at 📕

www.tugraz.at 📕

• lowering the refresh rate saves energy but produces more bit flips

- lowering the refresh rate saves energy but produces more bit flips

- $\rightarrow\,$  use ECC memory to mitigate bit flips

- lowering the refresh rate saves energy but produces more bit flips

- $\rightarrow\,$  use ECC memory to mitigate bit flips

- in the end: it's an optimization problem.

- lowering the refresh rate saves energy but produces more bit flips

- $\rightarrow\,$  use ECC memory to mitigate bit flips

- in the end: it's an optimization problem.

- too aggressive? bit flips will be possible

- lowering the refresh rate saves energy but produces more bit flips

- $\rightarrow\,$  use ECC memory to mitigate bit flips

- in the end: it's an optimization problem.

- too aggressive? bit flips will be possible

- too cautious? waste of energy

- lowering the refresh rate saves energy but produces more bit flips

- $\rightarrow\,$  use ECC memory to mitigate bit flips

- in the end: it's an optimization problem.

- too aggressive? bit flips will be possible

- too cautious? waste of energy

- what if the "too aggressive" changes over time?

- lowering the refresh rate saves energy but produces more bit flips

- $\rightarrow\,$  use ECC memory to mitigate bit flips

- in the end: it's an optimization problem.

- too aggressive? bit flips will be possible

- too cautious? waste of energy

- what if the "too aggressive" changes over time?

- what if attackers come up with slightly better attacks?

- lowering the refresh rate saves energy but produces more bit flips

- $\rightarrow\,$  use ECC memory to mitigate bit flips

- in the end: it's an optimization problem.

- too aggressive? bit flips will be possible

- too cautious? waste of energy

- what if the "too aggressive" changes over time?

- what if attackers come up with slightly better attacks?

- $\rightarrow\,$  difficult to optimize with an intelligent adversary

## We have ignored microarchitectural attacks for many many years:

We have ignored microarchitectural attacks for many many years:

• attacks on crypto

We have ignored microarchitectural attacks for many many years:

$\bullet$  attacks on crypto  $\rightarrow$  "software should be fixed"

- $\bullet$  attacks on crypto  $\rightarrow$  "software should be fixed"

- attacks on ASLR

- attacks on crypto  $\rightarrow$  "software should be fixed"

- $\bullet\,$  attacks on ASLR  $\rightarrow\,$  "ASLR is broken anyway"

- attacks on crypto  $\rightarrow$  "software should be fixed"

- attacks on ASLR  $\rightarrow$  "ASLR is broken anyway"

- attacks on SGX and TrustZone

- $\bullet\,$  attacks on crypto  $\rightarrow\,$  "software should be fixed"

- $\bullet$  attacks on ASLR  $\rightarrow$  "ASLR is broken anyway"

- $\bullet$  attacks on SGX and TrustZone  $\rightarrow$  "not part of the threat model"

- attacks on crypto  $\rightarrow$  "software should be fixed"

- $\bullet$  attacks on ASLR  $\rightarrow$  "ASLR is broken anyway"

- $\bullet$  attacks on SGX and TrustZone  $\rightarrow$  "not part of the threat model"

- Rowhammer attacks

- $\bullet\,$  attacks on crypto  $\rightarrow\,$  "software should be fixed"

- $\bullet$  attacks on ASLR  $\rightarrow$  "ASLR is broken anyway"

- $\bullet$  attacks on SGX and TrustZone  $\rightarrow$  "not part of the threat model"

- $\bullet$  Rowhammer attacks  $\rightarrow$  "only affects cheap sub-standard modules"

- attacks on crypto  $\rightarrow$  "software should be fixed"

- $\bullet$  attacks on ASLR  $\rightarrow$  "ASLR is broken anyway"

- $\bullet$  attacks on SGX and TrustZone  $\rightarrow$  "not part of the threat model"

- $\bullet$  Rowhammer attacks  $\rightarrow$  "only affects cheap sub-standard modules"

- $\rightarrow\,$  for years we solely optimized for performance

After learning about a side channel you realize:

Daniel Gruss — Graz University of Technology

After learning about a side channel you realize:

• the side channels were documented in the Intel manual

After learning about a side channel you realize:

- the side channels were documented in the Intel manual

- only now we understand the implications

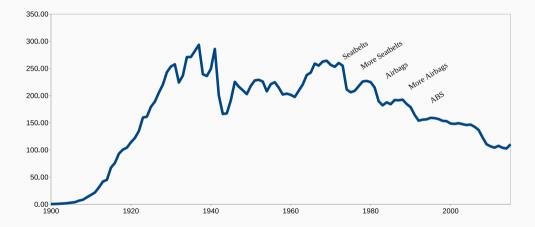

Motor Vehicle Deaths in U.S. by Year

Daniel Gruss — Graz University of Technology

• moral obligation to invest more time on defenses than on attacks

- moral obligation to invest more time on defenses than on attacks

- dangerous: we overlooked Meltdown and Spectre for decades

- moral obligation to invest more time on defenses than on attacks

- dangerous: we overlooked Meltdown and Spectre for decades

- we don't know all problems. do we know at least the most important subset?

- moral obligation to invest more time on defenses than on attacks

- dangerous: we overlooked Meltdown and Spectre for decades

- we don't know all problems. do we know at least the most important subset?

- are we hammering on a small subset of problems and forgot about the bigger picture?

Daniel Gruss — Graz University of Technology

### A unique chance to

• rethink processor design

### A unique chance to

- rethink processor design

- grow up, like other fields (car industry, construction industry)

### A unique chance to

- rethink processor design

- grow up, like other fields (car industry, construction industry)

- dedicate more time into identifying problems and not solely in mitigating known problems

# Microarchitectural Attacks:

## From the Basics to Arbitrary Read and Write Primitives without any Software Bugs

### **Daniel Gruss**

June 19, 2018

Graz University of Technology