# Microarchitectural Incontinence You would leak too if you were so fast!

Daniel Gruss Graz University of Technology

October 18, 2016 — Hacktivity

1

#### You know water races?

Daniel Gruss, Graz University of Technology October 18, 2016 — Hacktivity

### Going too fast

- CPU frequency i386  $\rightarrow$  Skylake:  $\times$  160

- DRAM module capacity  $KB \rightarrow GB: \times 1$  million

- DRAM manufacturing size  $\mu m \rightarrow nm$

### Going too fast

- CPU frequency i386  $\rightarrow$  Skylake:  $\times$  160

- DRAM module capacity KB  $\rightarrow$  GB:  $\times$  1 million

- DRAM manufacturing size  $\mu m \to nm$

Try a water race at  $160 \times$  speed with tiny cups

# Intel CPUs

- new microarchitectures yearly

- performance improvement  $\approx 5\%$

- very small optimizations: caches, branch prediction...

# Intel CPUs

- new microarchitectures yearly

- performance improvement  $\approx 5\%$

- very small optimizations: caches, branch prediction...

- $\rightarrow\,$  more and more leakage

# Whoami

- Daniel Gruss

- PhD Student, Graz University of Technology

- Twitter: @lavados

- Email: daniel.gruss@iaik.tugraz.at

#### • safe software infrastructure $\rightarrow$ no bugs, e.g., Heartbleed

- safe software infrastructure  $\rightarrow$  no bugs, e.g., Heartbleed

- does not mean safe execution

- **•** safe software infrastructure  $\rightarrow$  no bugs, e.g., Heartbleed

- does not mean safe execution

- information leaks because of the hardware it runs on

- $\hfill \,$  no "bug" in the sense of a mistake  $\rightarrow$  lots of performance optimizations

- **•** safe software infrastructure  $\rightarrow$  no bugs, e.g., Heartbleed

- does not mean safe execution

- information leaks because of the hardware it runs on

- $\hfill \,$  no "bug" in the sense of a mistake  $\rightarrow$  lots of performance optimizations

- ightarrow crypto and other sensitive info, e.g., keystrokes and mouse movements

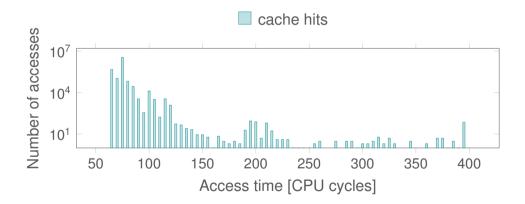

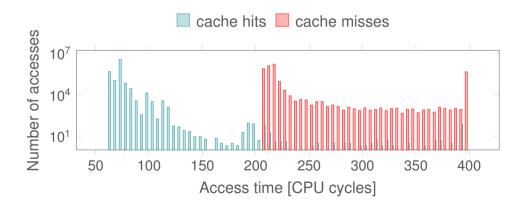

# Timing differences

# Timing differences

7

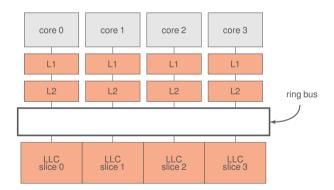

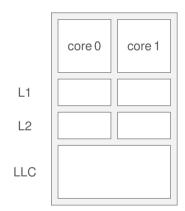

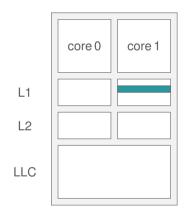

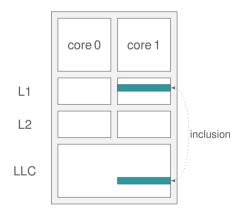

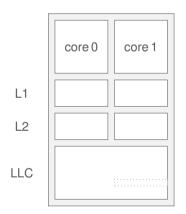

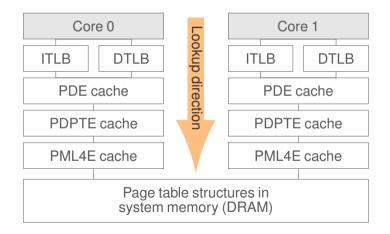

# Caches on Intel CPUs

- L1 and L2 are private

- Iast-level cache:

- divided in slices

- shared across cores

- inclusive

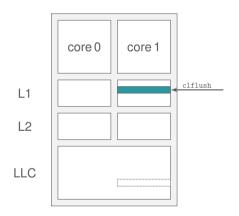

### Inclusive property

inclusive LLC: superset of L1 and L2

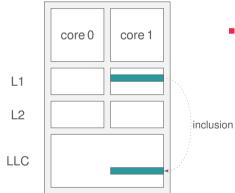

### Inclusive property

inclusive LLC: superset of L1 and L2

#### Inclusive property

inclusive LLC: superset of L1 and L2

### Inclusive property

• inclusive LLC: superset of L1 and L2

# Inclusive property

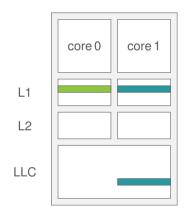

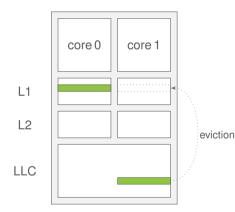

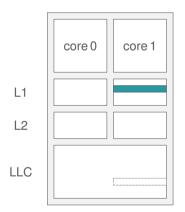

- inclusive LLC: superset of L1 and L2

- data evicted from the LLC is also evicted from L1 and L2

# Inclusive property

- inclusive LLC: superset of L1 and L2

- data evicted from the LLC is also evicted from L1 and L2

- a core can evict lines in the private L1

of another core

| address |     |        |  |

|---------|-----|--------|--|

| tag     | set | offset |  |

| <br> |

|------|

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

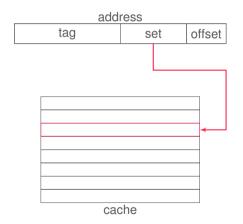

#### line loaded in a specific set depending on its address

- L1: virtually indexed

- L2, LLC: physically indexed

- line loaded in a specific set depending on its address

- L1: virtually indexed

- L2, LLC: physically indexed

- line loaded in a specific set depending on its address

- L1: virtually indexed

- L2, LLC: physically indexed

- several ways per set

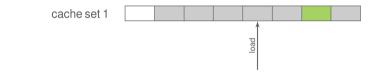

- line loaded in a specific set depending on its address

- L1: virtually indexed

- L2, LLC: physically indexed

- several ways per set

- replacement policy decides line to evict to store a new one

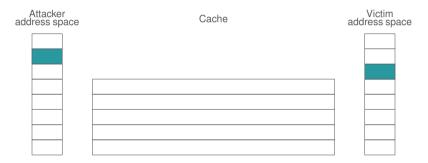

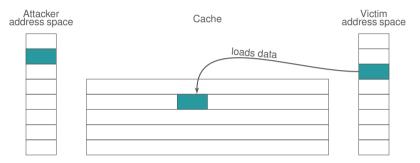

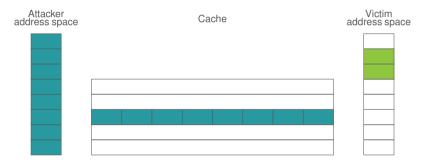

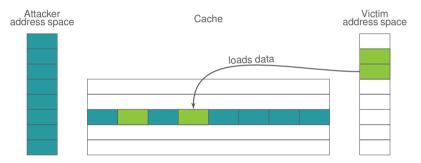

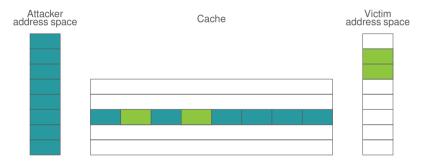

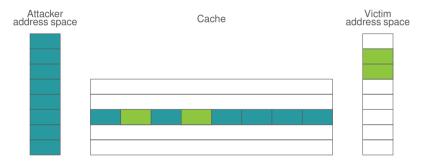

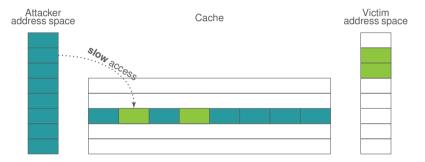

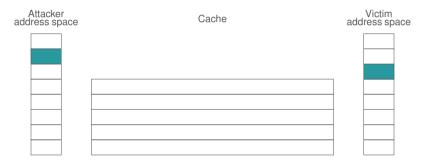

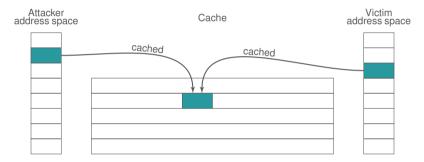

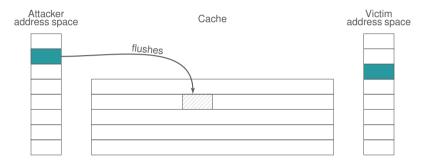

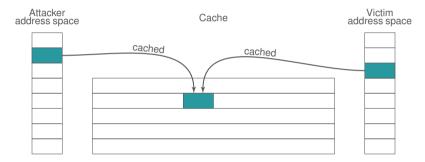

step 0: attacker maps shared library  $\rightarrow$  shared memory, shared in cache

step 0: attacker maps shared library  $\rightarrow$  shared memory, shared in cache

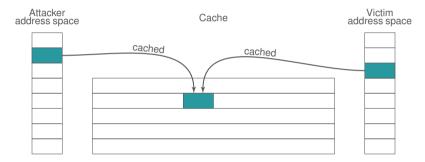

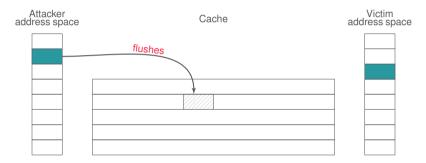

step 0: attacker maps shared library  $\rightarrow$  shared memory, shared in cache step 1: attacker flushes the shared line with clflush

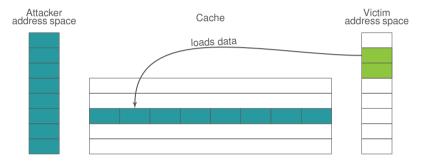

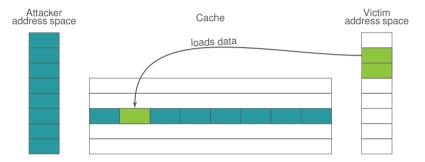

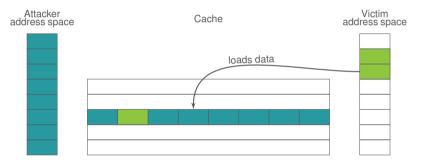

step 0: attacker maps shared library  $\rightarrow$  shared memory, shared in cache

step 1: attacker flushes the shared line with clflush

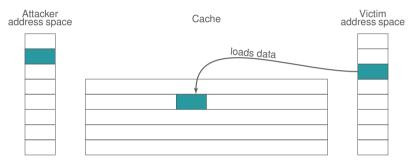

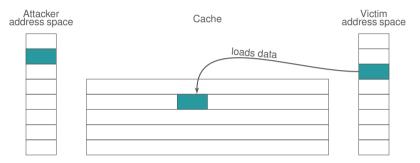

step 2: victim loads data while performing encryption

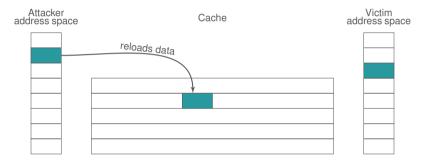

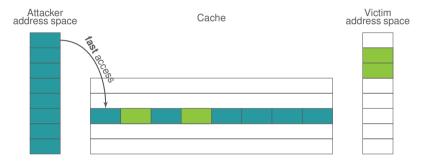

step 0: attacker maps shared library  $\rightarrow$  shared memory, shared in cache

- step 1: attacker flushes the shared line with clflush

- step 2: victim loads data while performing encryption

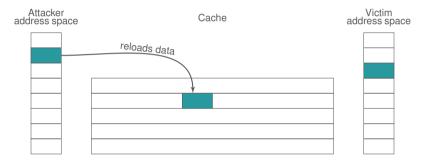

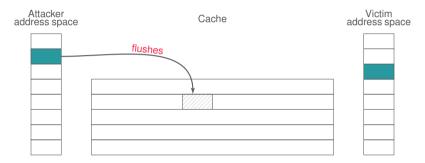

step 3: attacker reloads data  $\rightarrow$  fast access if the victim loaded the line

#### Flush+Reload: Applications

cross-VM side channel attacks on crypto algorithms:

- RSA: 96.7% of secret key bits in a single signature

- AES: full key recovery in 30000 dec. (a few seconds)

Y. Yarom and K. Falkner. "Flush+Reload: a High Resolution, Low Noise, L3 Cache Side-Channel Attack". In: USENIX Security Symposium. 2014.

B. Gülmezoğlu, M. S. Inci, T. Eisenbarth, and B. Sunar. "A Faster and More Realistic Flush+Reload Attack on AES". . In: COSADE'15. 2015.

D. Gruss, R. Spreitzer, and S. Mangard. "Cache Template Attacks: Automating Attacks on Inclusive Last-Level Caches". In: USENIX Security Symposium. 2015.

#### Flush+Reload: Applications

#### cross-VM side channel attacks on crypto algorithms:

- RSA: 96.7% of secret key bits in a single signature

- AES: full key recovery in 30000 dec. (a few seconds)

- Cache Template Attacks: automatically exploits cache-based information leakage

Y. Yarom and K. Falkner. "Flush+Reload: a High Resolution, Low Noise, L3 Cache Side-Channel Attack". In: USENIX Security Symposium. 2014.

B. Gülmezoğlu, M. S. Inci, T. Eisenbarth, and B. Sunar. "A Faster and More Realistic Flush+Reload Attack on AES". In: COSADE'15. 2015.

D. Gruss, R. Spreitzer, and S. Mangard. "Cache Template Attacks: Automating Attacks on Inclusive Last-Level Caches". In: USENIX Security Symposium. 2015.

https://github.com/IAIK/cache\_template\_attacks

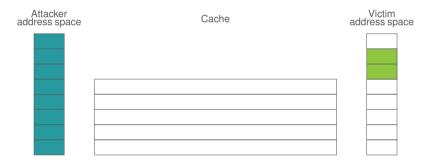

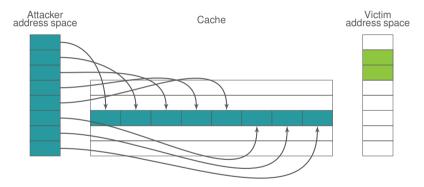

step 0: attacker fills the cache (prime)

step 0: attacker fills the cache (prime)

step 0: attacker fills the cache (prime)

step 0: attacker fills the cache (prime)

step 1: victim evicts cache lines while performing encryption

step 0: attacker fills the cache (prime)

step 1: victim evicts cache lines while performing encryption

step 0: attacker fills the cache (prime)

step 1: victim evicts cache lines while performing encryption

step 0: attacker fills the cache (prime)

step 1: victim evicts cache lines while performing encryption

step 0: attacker fills the cache (prime)

step 1: victim evicts cache lines while performing encryption

step 0: attacker fills the cache (prime)

step 1: victim evicts cache lines while performing encryption

step 2: attacker probes data to determine if the set was accessed

step 0: attacker fills the cache (prime)

step 1: victim evicts cache lines while performing encryption

step 2: attacker probes data to determine if the set was accessed

step 0: attacker fills the cache (prime)

step 1: victim evicts cache lines while performing encryption

step 2: attacker probes data to determine if the set was accessed

#### Prime+Probe: Applications

• cross-VM side channel attacks on crypto algorithms:

- El Gamal (sliding window): full key recovery in 12 min.

- tracking user behavior in the browser, in JavaScript

F. Liu, Y. Yarom, Q. Ge, G. Heiser, and R. B. Lee. "Last-Level Cache Side-Channel Attacks are Practical". In: S&P'15. 2015.

Y. Oren, V. P. Kemerlis, S. Sethumadhavan, and A. D. Keromytis. "The Spy in the Sandbox: Practical Cache Attacks in JavaScript and their Implications". In: CCS'15. 2015.

# Challenges with Prime+Probe

We need to evict caches lines without clflush or shared memory:

- 1. which addresses do we access to have congruent cache lines?

- 2. without any privilege?

- 3. and in which order do we access them?

# Challenges with Prime+Probe

We need to evict caches lines without clflush or shared memory:

- 1. which addresses do we access to have congruent cache lines?

- 2. without any privilege?

- 3. and in which order do we access them?

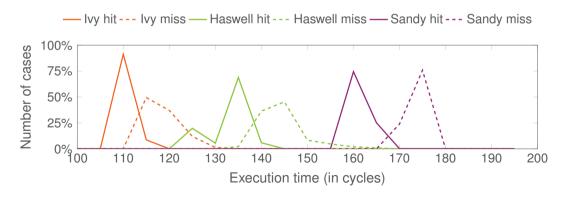

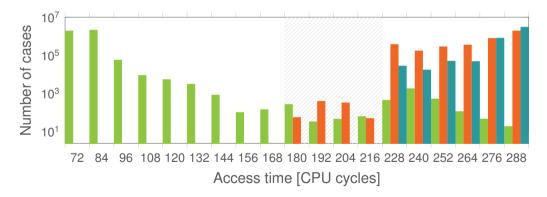

#### Stealthier cache attack: Flush+Flush

- motivation: detecting cache attacks with perf counters is not enough

- $\rightarrow\,$  Flush+Flush: new cache attack, based on <code>clflush</code> timing leakage

- $\rightarrow$  stealthier than Prime+Probe and Flush+Reload

- $\rightarrow$  faster than Prime+Probe and Flush+Reload

D. Gruss, C. Maurice, K. Wagner, and S. Mangard. "Flush+Flush: A Fast and Stealthy Cache Attack". In: DIMVA'16. 2016.

https://github.com/IAIK/flush\_flush

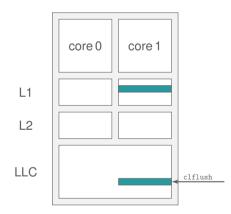

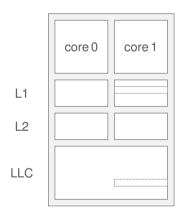

clflush on cached data

- clflush on cached data

- goes to LLC, flushes line

- clflush on cached data

- goes to LLC, flushes line

- clflush on cached data

- goes to LLC, flushes line

- flushes line in L1-L2

- clflush on cached data

- goes to LLC, flushes line

- flushes line in L1-L2

- $\rightarrow$  slow

- clflush on cached data

- goes to LLC, flushes line

- flushes line in L1-L2

- $\rightarrow$  slow

- clflush on non-cached data

- clflush on cached data

- goes to LLC, flushes line

- flushes line in L1-L2

- $\rightarrow$  slow

- clflush on non-cached data

- goes to LLC, does nothing

- clflush on cached data

- goes to LLC, flushes line

- flushes line in L1-L2

- $\rightarrow$  slow

- clflush on non-cached data

- goes to LLC, does nothing

- $\rightarrow$  fast

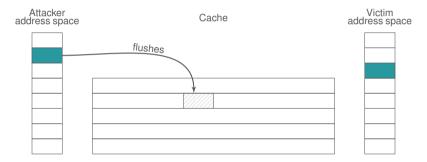

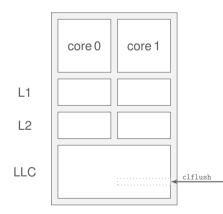

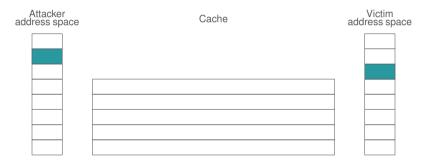

step 0: attacker maps shared library  $\rightarrow$  shared memory, shared in cache

step 0: attacker maps shared library  $\rightarrow$  shared memory, shared in cache

step 0: attacker maps shared library  $\rightarrow$  shared memory, shared in cache step 1: attacker flushes the shared line with <code>clflush</code>

step 0: attacker maps shared library  $\rightarrow$  shared memory, shared in cache

step 1: attacker flushes the shared line with clflush

step 2: victim loads data while performing encryption

step 0: attacker maps shared library  $\rightarrow$  shared memory, shared in cache

- step 1: attacker flushes the shared line with clflush

- step 2: victim loads data while performing encryption

step 3: attacker reloads data  $\rightarrow$  fast access if the victim loaded the line

step 0: attacker maps shared library  $\rightarrow$  shared memory, shared in cache

step 0: attacker maps shared library  $\rightarrow$  shared memory, shared in cache

step 0: attacker maps shared library  $\rightarrow$  shared memory, shared in cache step 1: attacker flushes the shared line

step 0: attacker maps shared library  $\rightarrow$  shared memory, shared in cache

- step 1: attacker flushes the shared line

- step 2: victim loads data while performing encryption

step 0: attacker maps shared library  $\rightarrow$  shared memory, shared in cache

- step 1: attacker flushes the shared line

- step 2: victim loads data while performing encryption

step 3: attacker flushes data  $\rightarrow$  high execution time if the victim loaded the line

#### Even more timing leakage with clflush

# ARMageddon: Challenges of ARM

- 1. ARM v7 CPUs have no flush instruction

- 2. replacement policy is pseudo-random

- 3. cycle-accurate timings require root

- 4. last-level caches are not inclusive

- 5. multiple CPUs do not share a cache

M. Lipp, D. Gruss, R. Spreitzer, C. Maurice, and S. Mangard. "ARMageddon: Last-Level Cache Attacks on Mobile Devices". In: USENIX Security Symposium. 2016.

# ARMageddon

All cache attacks from Intel x86 applicable are to ARM devices

- covert channel up to 1 Mbps

- ightarrow 2-3 orders of magnitude faster than previous work

- side channels

- monitor taps and swipe events, keystrokes

- AES T-table implementation of Bounty Castle 1.5

#### What about...

... other caches? Yes, they leak too.

# Intel being overspecific

#### NOTE

#### Intel being overspecific

#### NOTE

Using the PREFETCH instruction is **recommended** only if data does not fit in cache.

# Intel being overspecific

#### NOTE

Using the PREFETCH instruction is **recommended** only if data does not fit in cache. Use of software prefetch **should** be limited to memory addresses that are managed or owned within the application context.

## Intel being overspecific

#### NOTE

Using the PREFETCH instruction is **recommended** only if data does not fit in cache. Use of software prefetch **should** be limited to memory addresses that are managed or owned within the application context. Prefetching to addresses that are **not mapped to physical** pages can experience **non-deterministic** performance penalty.

## Intel being overspecific

# Software prefetching

prefetch instructions are somewhat unusual

- Hints can be ignored by the CPU

- Do not check privileges or cause exceptions

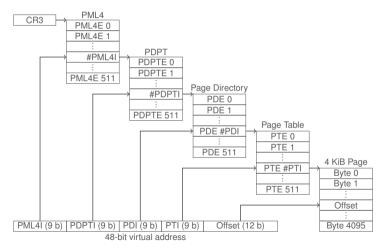

## Address translation on x86-64

27

## Solution: Address Translation Caches

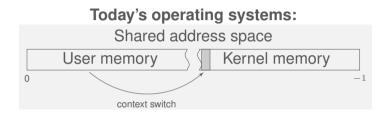

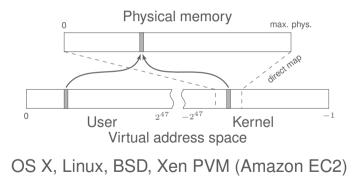

## Kernel is mapped in every process

29

## Address-Space Layout Randomization (ASLR)

- Kernel and drivers at randomized offsets in virtual memory

- Mitigates code reuse attacks e.g. return-oriented-programming

- Attacks based on read primitives or write primitives

## Address-Space Layout Randomization (ASLR)

- Kernel and drivers at randomized offsets in virtual memory

- Mitigates code reuse attacks e.g. return-oriented-programming

- Attacks based on read primitives or write primitives

- But: leaking kernel/driver addresses defeats ASLR

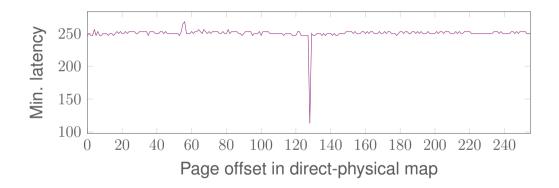

## Kernel direct-physical map

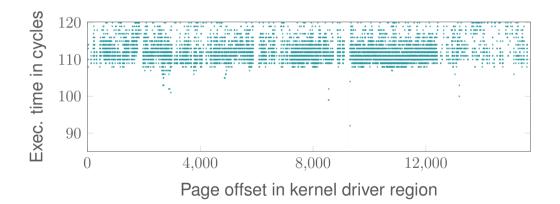

## Locate Kernel Driver (defeat KASLR)

## Defeating SMAP/SMEP

- Get direct-physical-map address of userspace address

- $\rightarrow\,$  jump there (it's executable)

- $\rightarrow\,$  or: switch to stack there

Known as "ret2dir" attacks

V. P. Kemerlis, M. Polychronakis, and A. D. Keromytis. "ret2dir: Rethinking kernel isolation". In: USENIX Security Symposium. 2014, pp. 957–972.

#### Prefetching via direct-physical map

#### Beyond cache attacks

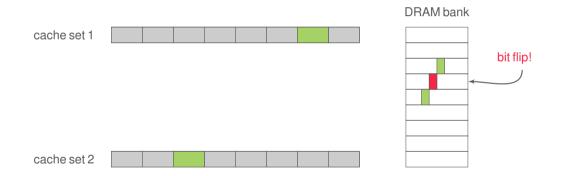

talking about DRAM:

- Rowhammer.js

- DRAM side-channel attacks

D. Gruss, C. Maurice, and S. Mangard. "Rowhammer.js: A Remote Software-Induced Fault Attack in JavaScript". In: DIMVA'16. 2016.

P. Pessl, D. Gruss, C. Maurice, M. Schwarz, and S. Mangard. "DRAMA: Exploiting DRAM Addressing for Cross-CPU Attacks". In: USENIX Security Symposium. 2016.

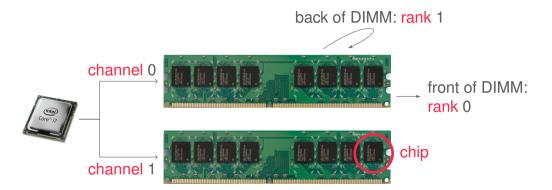

- bits in cells in rows

- access: activate row, copy to row buffer

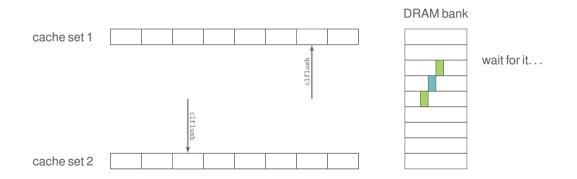

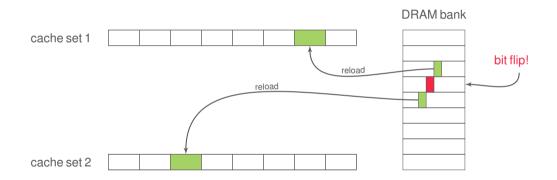

## **DRAM** refresh

- cells leak  $\rightarrow$  repetitive refresh necessary

- refresh  $\approx$  reading (destructive) + writing same data again

- maximum interval between refreshes to guarantee data integrity

### **DRAM** refresh

- cells leak  $\rightarrow$  repetitive refresh necessary

- refresh  $\approx$  reading (destructive) + writing same data again

- maximum interval between refreshes to guarantee data integrity

- $\hfill \ensuremath{\,\,^{\circ}}$  cells leak faster upon proximate accesses  $\rightarrow$  Rowhammer

#### **DRAM** bank

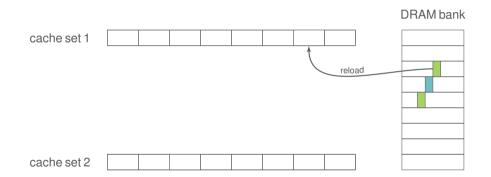

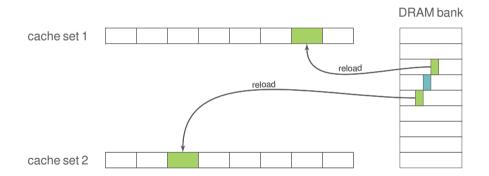

## Rowhammer without clflush?

- idea: avoid clflush to be independent of specific instructions  $\rightarrow$  no clflush in JavaScript

## Rowhammer without clflush?

- idea: avoid clflush to be independent of specific instructions  $\rightarrow$  no clflush in JavaScript

- our approach: use regular memory accesses for eviction

- $\rightarrow$  techniques from cache attacks!

- idea: avoid clflush to be independent of specific instructions  $\rightarrow$  no clflush in JavaScript

- our approach: use regular memory accesses for eviction

- $\rightarrow$  techniques from cache attacks!

- $\rightarrow$  Rowhammer, Prime+Probe style!

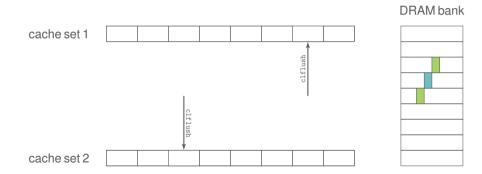

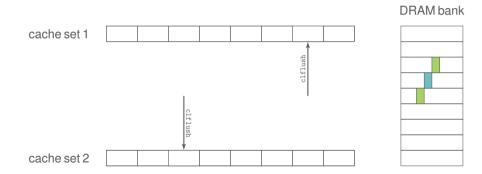

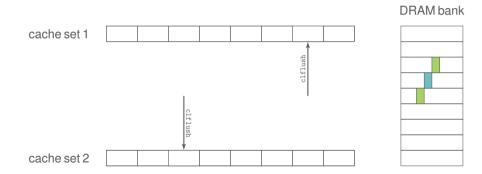

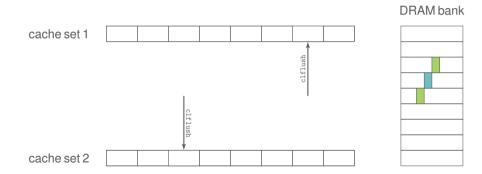

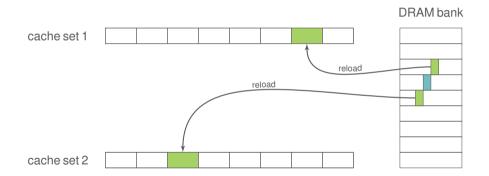

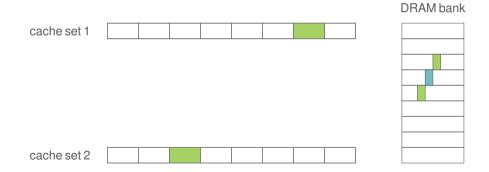

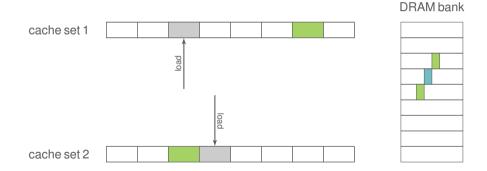

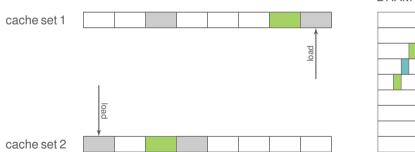

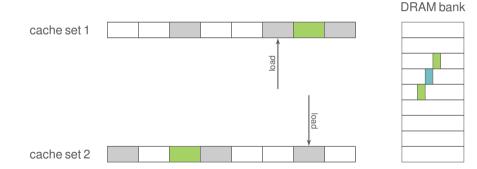

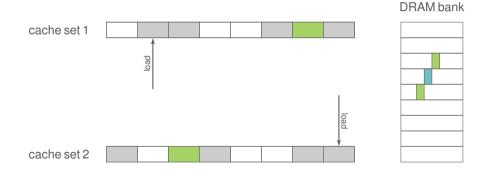

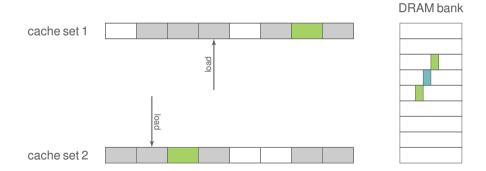

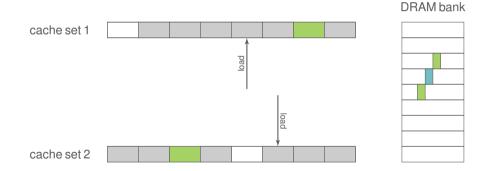

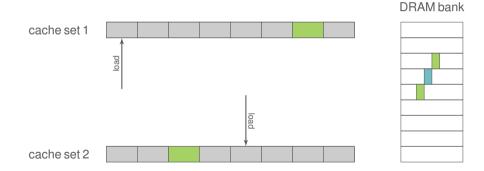

#### DRAM bank

Daniel Gruss, Graz University of Technology October 18, 2016 — Hacktivity

## Requirements for Rowhammer

- 1. uncached memory accesses: need to reach DRAM

- 2. fast memory accesses: race against the next row refresh

## Requirements for Rowhammer

- 1. uncached memory accesses: need to reach DRAM

- 2. fast memory accesses: race against the next row refresh

- $\rightarrow\,$  optimize the eviction rate and the timing

- 1. how to get accurate timing in JS?

- 2. how to get physical addresses in JS?

- 3. which physical addresses to access?

- 4. in which order to access them?

- 1. how to get accurate timing in JS?  $\rightarrow$  easy

- 2. how to get physical addresses in JS?

- 3. which physical addresses to access?

- 4. in which order to access them?

- 1. how to get accurate timing in JS?  $\rightarrow$  easy

- 2. how to get physical addresses in JS?  $\rightarrow$  we solved this

- 3. which physical addresses to access?

- 4. in which order to access them?

- 1. how to get accurate timing in JS?  $\rightarrow$  easy

- 2. how to get physical addresses in JS?  $\rightarrow$  we solved this

- 3. which physical addresses to access?  $\rightarrow$  we solved this

- 4. in which order to access them?

- 1. how to get accurate timing in JS?  $\rightarrow$  easy

- 2. how to get physical addresses in JS?  $\rightarrow$  we solved this

- 3. which physical addresses to access?  $\rightarrow$  we solved this

- 4. in which order to access them?  $\rightarrow$  we solved this

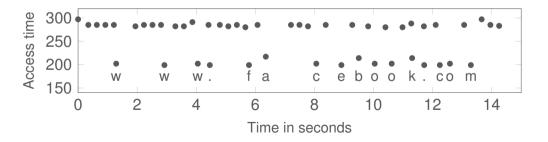

## How to get accurate timing in JavaScript?

native code: rdtsc

JavaScript: window.performance.now()

## How to get accurate timing in JavaScript?

- native code: rdtsc

- JavaScript: window.performance.now()

- recent patch: time rounded to 5 microseconds

- still works: we measure millions of accesses

#### Physical addresses and DRAM

- fixed map: physical addresses  $\rightarrow$  DRAM cells

- undocumented for Intel

- reverse-engineering for Sandy Bridge

- and by us for Sandy, Ivy, Haswell, Skylake,...

M. Seaborn. How physical addresses map to rows and banks in DRAM. http://lackingrhoticity.blogspot.com/2015/05/how-physical-addresses-map-to-rows-and-banks.html. Retrieved on July 20, 2015. 2015.

P. Pessl, D. Gruss, C. Maurice, M. Schwarz, and S. Mangard. "DRAMA: Exploiting DRAM Addressing for Cross-CPU Attacks". In: USENIX Security Symposium. 2016.

### Physical addresses and JavaScript

- OS optimization: use 2MB pages

- last 21 bits (2MB) of physical address

- I ast 21 bits (2MB) of virtual address

D. Gruss, D. Bidner, and S. Mangard. "Practical Memory Deduplication Attacks in Sandboxed Javascript". In: ESORICS'15. 2015.

### Physical addresses and JavaScript

- OS optimization: use 2MB pages

- last 21 bits (2MB) of physical address

- Iast 21 bits (2MB) of virtual address

- I ast 21 bits (2MB) of JS array indices

D. Gruss, D. Bidner, and S. Mangard. "Practical Memory Deduplication Attacks in Sandboxed Javascript". In: ESORICS'15. 2015.

### Physical addresses and JavaScript

- OS optimization: use 2MB pages

- last 21 bits (2MB) of physical address

- I ast 21 bits (2MB) of virtual address

- I ast 21 bits (2MB) of JS array indices

- several DRAM rows per 2MB page

- several congruent addresses per 2MB page

D. Gruss, D. Bidner, and S. Mangard. "Practical Memory Deduplication Attacks in Sandboxed Javascript". In: ESORICS'15. 2015.

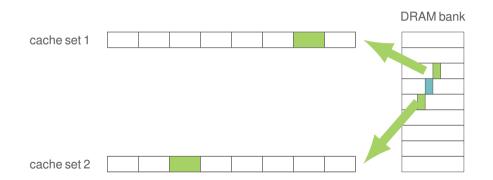

## Which physical addresses to access?

"LRU eviction":

- assume that cache uses LRU replacement

- accessing n addresses from the same cache set to evict an n-way set

- using the reverse-engineered last-level cache addressing function

C. Maurice, N. Le Scouarnec, C. Neumann, O. Heen, and A. Francillon. "Reverse Engineering Intel Complex Addressing Using Performance Counters". In: RAID. 2015.

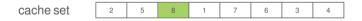

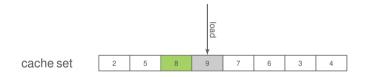

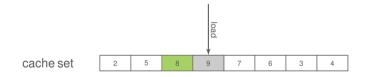

"LRU eviction" memory accesses

"LRU eviction" memory accesses

LRU replacement policy: oldest entry first

"LRU eviction" memory accesses

- LRU replacement policy: oldest entry first

- timestamps for every cache line

"LRU eviction" memory accesses

- LRU replacement policy: oldest entry first

- timestamps for every cache line

- access updates timestamp

"LRU eviction" memory accesses

- LRU replacement policy: oldest entry first

- timestamps for every cache line

- access updates timestamp

"LRU eviction" memory accesses

- LRU replacement policy: oldest entry first

- timestamps for every cache line

- access updates timestamp

"LRU eviction" memory accesses

- LRU replacement policy: oldest entry first

- timestamps for every cache line

- access updates timestamp

"LRU eviction" memory accesses

- LRU replacement policy: oldest entry first

- timestamps for every cache line

- access updates timestamp

# Replacement policy on older CPUs

"LRU eviction" memory accesses

- LRU replacement policy: oldest entry first

- timestamps for every cache line

- access updates timestamp

# Replacement policy on older CPUs

"LRU eviction" memory accesses

- LRU replacement policy: oldest entry first

- timestamps for every cache line

- access updates timestamp

# Replacement policy on older CPUs

"LRU eviction" memory accesses

- LRU replacement policy: oldest entry first

- timestamps for every cache line

- access updates timestamp

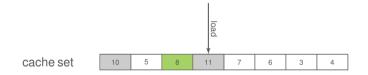

"LRU eviction" memory accesses

no LRU replacement on recent CPUs

"LRU eviction" memory accesses

no LRU replacement on recent CPUs

"LRU eviction" memory accesses

no LRU replacement on recent CPUs

"LRU eviction" memory accesses

no LRU replacement on recent CPUs

"LRU eviction" memory accesses

no LRU replacement on recent CPUs

"LRU eviction" memory accesses

no LRU replacement on recent CPUs

"LRU eviction" memory accesses

no LRU replacement on recent CPUs

"LRU eviction" memory accesses

no LRU replacement on recent CPUs

"LRU eviction" memory accesses

no LRU replacement on recent CPUs

"LRU eviction" memory accesses

- no LRU replacement on recent CPUs

- only 75% success rate on Haswell

"LRU eviction" memory accesses

- no LRU replacement on recent CPUs

- only 75% success rate on Haswell

- more accesses  $\rightarrow$  higher success rate, but too slow

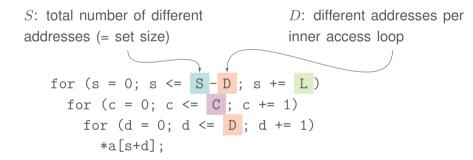

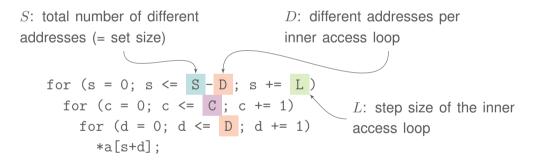

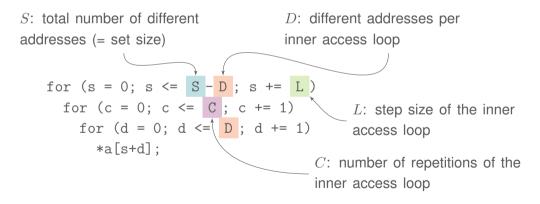

Write eviction strategies as:  $\mathcal{P}$ -C-D-L-S

S: total number of different addresses (= set size)

$$\bullet \mathcal{P} - 2 - 2 - 1 - 4 \to 1, 2, 1, 2, 2, 3, 2, 3, 3, 4, 3, 4$$

•

$$\mathcal{P}$$

-2-2-1-4  $\rightarrow$  1, 2, 1, 2, 2, 3, 2, 3, 3, 4, 3, 4  $\sim S = 4$

•

$$\mathcal{P}$$

-2-2-1-4  $\rightarrow$  1, 2, 1, 2, 2, 3, 2, 3, 3, 4, 3, 4  $S$

•

$$\mathcal{P}$$

-2-2-1-4  $\rightarrow$  (1, 2, (1, 2, 2, 3, 2, 3, 3, 4, 3, 4)  $S = 4$

$D = 2$

•

$$\mathcal{P}$$

-2-2-1-4  $\rightarrow$  1, 2, 1, 2, 2, 3, 2, 3, 3, 4, 3, 4

$D=2$   $C=2$

•

$$\mathcal{P}$$

-2-2-1-4  $\rightarrow$  1, 2, 1, 2, 2, 3, 2, 3, 3, 4, 3, 4

$L = 1$   $D = 2$   $C = 2$

•

$$\mathcal{P}$$

-2-2-1-4  $\rightarrow$  1, 2, 1, 2, 2, 3, 2, 3, 3, 4, 3, 4

$L = 1$   $D = 2$   $C = 2$

•  $\mathcal{P}$ -1-1-1-4  $\rightarrow$  1, 2, 3, 4  $\rightarrow$  LRU eviction with set size 4

We evaluated more than 10000 strategies...

| strategy              | # accesses | eviction rate | loop time |

|-----------------------|------------|---------------|-----------|

| P-1-1-17              | 17         |               |           |

| $\mathcal{P}$ -1-1-20 | 20         |               |           |

We evaluated more than 10000 strategies...

| strategy              | # accesses | eviction rate | loop time |

|-----------------------|------------|---------------|-----------|

| P-1-1-17              | 17         | 74.46% 🗡      |           |

| $\mathcal{P}$ -1-1-20 | 20         | 99.82% 🗸      |           |

We evaluated more than 10000 strategies...

| strategy              | # accesses | eviction rate | loop time |

|-----------------------|------------|---------------|-----------|

| P-1-1-17              | 17         | 74.46% 🗡      | 307 ns 🗸  |

| $\mathcal{P}$ -1-1-20 | 20         | 99.82% 🗸      | 934 ns 🗡  |

We evaluated more than 10000 strategies...

| strategy                | # accesses | eviction rate | loop time |

|-------------------------|------------|---------------|-----------|

| $\mathcal{P}$ -1-1-1-17 | 17         | 74.46% 🗡      | 307 ns 🗸  |

| $\mathcal{P}$ -1-1-20   | 20         | 99.82% 🗸      | 934 ns 🗡  |

| $\mathcal{P}$ -2-1-1-17 | 34         |               |           |

We evaluated more than 10000 strategies...

| strategy                | # accesses | eviction rate | loop time |

|-------------------------|------------|---------------|-----------|

| $\mathcal{P}$ -1-1-1-17 | 17         | 74.46% 🗡      | 307 ns 🗸  |

| $\mathcal{P}$ -1-1-20   | 20         | 99.82% 🗸      | 934 ns 🗡  |

| $\mathcal{P}$ -2-1-1-17 | 34         | 99.86% 🗸      |           |

We evaluated more than 10000 strategies...

| strategy                | # accesses | eviction rate | loop time |

|-------------------------|------------|---------------|-----------|

| P-1-1-17                | 17         | 74.46% 🗡      | 307 ns 🗸  |

| $\mathcal{P}$ -1-1-20   | 20         | 99.82% 🗸      | 934 ns 🗡  |

| $\mathcal{P}$ -2-1-1-17 | 34         | 99.86% 🗸      | 191 ns 🗸  |

We evaluated more than 10000 strategies...

| strategy                | # accesses | eviction rate | loop time |

|-------------------------|------------|---------------|-----------|

| P-1-1-17                | 17         | 74.46% 🗡      | 307 ns 🗸  |

| $\mathcal{P}$ -1-1-20   | 20         | 99.82% 🗸      | 934 ns 🗡  |

| $\mathcal{P}$ -2-1-1-17 | 34         | 99.86% 🗸      | 191 ns 🗸  |

| $\mathcal{P}$ -2-2-1-17 | 64         |               |           |

We evaluated more than 10000 strategies...

| strategy                | # accesses | eviction rate | loop time |

|-------------------------|------------|---------------|-----------|

| P-1-1-17                | 17         | 74.46% 🗡      | 307 ns 🗸  |

| $\mathcal{P}$ -1-1-20   | 20         | 99.82% 🗸      | 934 ns 🗡  |

| $\mathcal{P}$ -2-1-1-17 | 34         | 99.86% 🗸      | 191 ns 🗸  |

| $\mathcal{P}$ -2-2-1-17 | 64         | 99.98% 🗸      |           |

We evaluated more than 10000 strategies...

| strategy                | # accesses | eviction rate | loop time |

|-------------------------|------------|---------------|-----------|

| P-1-1-17                | 17         | 74.46% 🗡      | 307 ns 🗸  |

| $\mathcal{P}$ -1-1-20   | 20         | 99.82% 🗸      | 934 ns 🗡  |

| $\mathcal{P}$ -2-1-1-17 | 34         | 99.86% 🗸      | 191 ns 🗸  |

| $\mathcal{P}$ -2-2-1-17 | 64         | 99.98% 🗸      | 180 ns 🗸  |

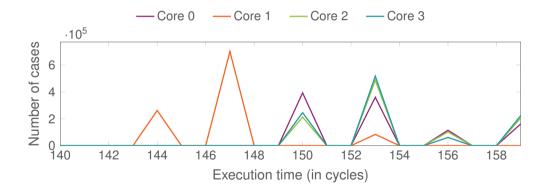

# Cache eviction strategies: Evaluation

We evaluated more than 10000 strategies...

| strategy                | # accesses | eviction rate | loop time |

|-------------------------|------------|---------------|-----------|

| P-1-1-17                | 17         | 74.46% 🗡      | 307 ns 🗸  |

| $\mathcal{P}$ -1-1-20   | 20         | 99.82% 🗸      | 934 ns 🗡  |

| $\mathcal{P}$ -2-1-1-17 | 34         | 99.86% 🗸      | 191 ns 🗸  |

| $\mathcal{P}$ -2-2-1-17 | 64         | 99.98% 🗸      | 180 ns 🗸  |

$\rightarrow$  more accesses, smaller execution time?

Executed in a loop, on a Haswell with a 16-way last-level cache

P-1-1-1-17 (17 accesses, 307ns)

#### P-2-1-1-17 (34 accesses, 191ns)

#### *P*-1-1-17 (17 accesses, 307ns)

### P-2-1-1-17 (34 accesses, 191ns)

#### *P*-1-1-17 (17 accesses, 307ns)

| Miss       | Miss       |

|------------|------------|

| (intended) | (intended) |

### P-2-1-1-17 (34 accesses, 191ns)

#### *P*-1-1-17 (17 accesses, 307ns)

| Miss<br>(intended) | Miss<br>(intended) | н |

|--------------------|--------------------|---|

|--------------------|--------------------|---|

### P-2-1-1-17 (34 accesses, 191ns)

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss<br>(intended) | Miss<br>(intended) | н | Miss |

|--------------------|--------------------|---|------|

|--------------------|--------------------|---|------|

## P-2-1-1-17 (34 accesses, 191ns)

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss<br>(intended) | Miss<br>(intended) | н | Miss |

|--------------------|--------------------|---|------|

|--------------------|--------------------|---|------|

## P-2-1-1-17 (34 accesses, 191ns)

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss<br>(intended) | Miss<br>(intended) | н | Miss |

|--------------------|--------------------|---|------|

|--------------------|--------------------|---|------|

## P-2-1-1-17 (34 accesses, 191ns)

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss<br>(intended) | Miss<br>(intended) | н |  | Miss |  |

|--------------------|--------------------|---|--|------|--|

|--------------------|--------------------|---|--|------|--|

## P-2-1-1-17 (34 accesses, 191ns)

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss<br>(intended) | Miss<br>(intended) | н |  | Miss |  |

|--------------------|--------------------|---|--|------|--|

|--------------------|--------------------|---|--|------|--|

## P-2-1-1-17 (34 accesses, 191ns)

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss<br>(intended) | Miss<br>(intended) | н | Miss |

|--------------------|--------------------|---|------|

|--------------------|--------------------|---|------|

## P-2-1-1-17 (34 accesses, 191ns)

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss<br>(intended) | Miss<br>(intended) | н | Miss |

|--------------------|--------------------|---|------|

|--------------------|--------------------|---|------|

## P-2-1-1-17 (34 accesses, 191ns)

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss Miss<br>(intended) (intended) | н | Miss | Miss |

|------------------------------------|---|------|------|

|------------------------------------|---|------|------|

### P-2-1-1-17 (34 accesses, 191ns)

| Miss<br>(intended) | Miss<br>(intended) |  | H | н | н | н |  | 1 | н | н | H |  | Miss |

|--------------------|--------------------|--|---|---|---|---|--|---|---|---|---|--|------|

|--------------------|--------------------|--|---|---|---|---|--|---|---|---|---|--|------|

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss Miss<br>(intended) (intended) | н | Miss | Miss |

|------------------------------------|---|------|------|

|------------------------------------|---|------|------|

### P-2-1-1-17 (34 accesses, 191ns)

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss Miss<br>(intended) (intended) | н | Miss | Miss |

|------------------------------------|---|------|------|

|------------------------------------|---|------|------|

### P-2-1-1-17 (34 accesses, 191ns)

#### P-1-1-1-17 (17 accesses, 307ns)

| (ir | Miss<br>itended) | Miss<br>(intended) | н | Miss | Miss |

|-----|------------------|--------------------|---|------|------|

|-----|------------------|--------------------|---|------|------|

### P-2-1-1-17 (34 accesses, 191ns)

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss Miss H<br>(intended) (intended) | Miss | Miss | Miss |

|--------------------------------------|------|------|------|

|--------------------------------------|------|------|------|

## P-2-1-1-17 (34 accesses, 191ns)

| Miss Miss<br>(intended) (intended) | нынынын | Miss HIHIHH |

|------------------------------------|---------|-------------|

|------------------------------------|---------|-------------|

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss Miss<br>(intended) (intended) | н | Miss | Miss | Miss |

|------------------------------------|---|------|------|------|

|------------------------------------|---|------|------|------|

### P-2-1-1-17 (34 accesses, 191ns)

| Miss Miss<br>(intended) (intended) | HHHHHHHH Miss | ннннн |

|------------------------------------|---------------|-------|

|------------------------------------|---------------|-------|

### P-1-1-1-17 (17 accesses, 307ns)

| Miss Miss<br>(intended) (intended) | н | Miss | Miss | Miss |

|------------------------------------|---|------|------|------|

|------------------------------------|---|------|------|------|

## P-2-1-1-17 (34 accesses, 191ns)

| Miss Miss<br>(intended) (intended) | нынынын | Miss HHHHHH |

|------------------------------------|---------|-------------|

|------------------------------------|---------|-------------|

### P-1-1-1-17 (17 accesses, 307ns)

| Miss Miss<br>(intended) (intended) | н | Miss | Miss | Miss |

|------------------------------------|---|------|------|------|

|------------------------------------|---|------|------|------|

## P-2-1-1-17 (34 accesses, 191ns)

| Miss Miss<br>(intended) (intended) | HHHHHHHH Miss | ныннын |

|------------------------------------|---------------|--------|

|------------------------------------|---------------|--------|

### P-1-1-1-17 (17 accesses, 307ns)

| Miss Miss<br>(intended) (intended) | н | Miss | Miss | Miss |

|------------------------------------|---|------|------|------|

|------------------------------------|---|------|------|------|

## P-2-1-1-17 (34 accesses, 191ns)

| Miss Miss<br>(intended) (intended) | ныныныны | Miss | ныныны |

|------------------------------------|----------|------|--------|

|------------------------------------|----------|------|--------|

### P-1-1-1-17 (17 accesses, 307ns)

| Miss Miss<br>(intended) (intended) | н | Miss | Miss | Miss | ŀ |

|------------------------------------|---|------|------|------|---|

|------------------------------------|---|------|------|------|---|

### P-2-1-1-17 (34 accesses, 191ns)

| Miss Miss<br>(intended) (intended) | HHHHHHH Miss | HHHHHHH Miss |

|------------------------------------|--------------|--------------|

|------------------------------------|--------------|--------------|

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss Miss<br>(intended) (intended) | н | Miss | Miss | Miss | н | Miss |

|------------------------------------|---|------|------|------|---|------|

|------------------------------------|---|------|------|------|---|------|

#### P-2-1-1-17 (34 accesses, 191ns)

| Miss Miss<br>(intended) (intended) | HIHHHHHHH Miss | HHHHHHHH Miss |

|------------------------------------|----------------|---------------|

|------------------------------------|----------------|---------------|

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss Miss<br>(intended) (intended) | н | Miss | Miss | Miss | н | Miss |

|------------------------------------|---|------|------|------|---|------|

|------------------------------------|---|------|------|------|---|------|

#### P-2-1-1-17 (34 accesses, 191ns)

| Miss<br>(intended) | Miss<br>(intended) | нынынын | Miss | нынынын | H Miss | н |

|--------------------|--------------------|---------|------|---------|--------|---|

|--------------------|--------------------|---------|------|---------|--------|---|

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss Miss<br>(intended) (intended) | н | Miss | Miss | Miss | н | Miss |

|------------------------------------|---|------|------|------|---|------|

|------------------------------------|---|------|------|------|---|------|

#### P-2-1-1-17 (34 accesses, 191ns)

| Miss Miss<br>(intended) (intended | нынынын | Miss | нынынын | Miss | нн |

|-----------------------------------|---------|------|---------|------|----|

|-----------------------------------|---------|------|---------|------|----|

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss Miss<br>(intended) (intended) | н | Miss | Miss | Miss | н | Miss |

|------------------------------------|---|------|------|------|---|------|

|------------------------------------|---|------|------|------|---|------|

### P-2-1-1-17 (34 accesses, 191ns)

| Miss Miss<br>(intended) (intended) | нананан | Miss | нынынын | Miss H | нн |

|------------------------------------|---------|------|---------|--------|----|

|------------------------------------|---------|------|---------|--------|----|

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss Miss<br>(intended) (intended) | н | Miss | Miss | Miss | н | Miss |

|------------------------------------|---|------|------|------|---|------|

|------------------------------------|---|------|------|------|---|------|

### P-2-1-1-17 (34 accesses, 191ns)

| Miss Miss<br>(intended) (intended) | HHHHHHHH Miss | HHHHHHH Miss | нннн |

|------------------------------------|---------------|--------------|------|

|------------------------------------|---------------|--------------|------|

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss Miss<br>(intended) (intended) | н | Miss | Miss | Miss | н | Miss |

|------------------------------------|---|------|------|------|---|------|

|------------------------------------|---|------|------|------|---|------|

### P-2-1-1-17 (34 accesses, 191ns)

| Miss Miss<br>(intended) (intended) | HHHHHHH Miss | нынынын | Miss HHHHH |

|------------------------------------|--------------|---------|------------|

|------------------------------------|--------------|---------|------------|

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss Miss<br>(intended) (intended) | н | Miss | Miss | Miss | н | Miss |

|------------------------------------|---|------|------|------|---|------|

|------------------------------------|---|------|------|------|---|------|

### P-2-1-1-17 (34 accesses, 191ns)

| Miss Miss<br>(intended) (intended) | HHHHHHH Miss | нөнөнөн | Miss HHHHHH |

|------------------------------------|--------------|---------|-------------|

|------------------------------------|--------------|---------|-------------|

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss Miss<br>(intended) (intended) | H Miss | Miss | Miss | H Miss | Miss |

|------------------------------------|--------|------|------|--------|------|

|------------------------------------|--------|------|------|--------|------|

## P-2-1-1-17 (34 accesses, 191ns)

| Miss Miss<br>(intended) (intended) | HHHHHHHH Miss | нынынын | Miss HHHHHHH |

|------------------------------------|---------------|---------|--------------|

|------------------------------------|---------------|---------|--------------|

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss Miss<br>(intended) (intended) | H Miss | Miss | Miss | H Miss | Miss |

|------------------------------------|--------|------|------|--------|------|

|------------------------------------|--------|------|------|--------|------|

### P-2-1-1-17 (34 accesses, 191ns)

| Miss<br>(intended) | Miss<br>(intended) | нынынын | Miss | нынынын | Miss HIHHHHHHH |

|--------------------|--------------------|---------|------|---------|----------------|

|--------------------|--------------------|---------|------|---------|----------------|

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss<br>(intended) | Miss<br>(intended) | Miss | Miss | Miss | н | Miss | Miss | Miss |

|--------------------|--------------------|------|------|------|---|------|------|------|

|--------------------|--------------------|------|------|------|---|------|------|------|

### *P*-2-1-1-17 (34 accesses, 191ns)

Miss (intended) (intended) However the Miss

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss<br>(intended) | Miss<br>(intended) | Miss | Miss | Miss | н | Miss | Miss | Miss |

|--------------------|--------------------|------|------|------|---|------|------|------|

|--------------------|--------------------|------|------|------|---|------|------|------|

### *P*-2-1-1-17 (34 accesses, 191ns)

Miss (intended) (intended) whether Miss whether Miss whether Miss

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss<br>(intended) | Miss<br>(intended) | Miss | Miss | Miss | н | Miss | Miss | Miss |

|--------------------|--------------------|------|------|------|---|------|------|------|

|--------------------|--------------------|------|------|------|---|------|------|------|

### *P*-2-1-1-17 (34 accesses, 191ns)

Mas Mas (rintended) Polytologic Mas Production Mas Production

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss<br>(intended) | Miss<br>(intended) | Miss | Miss | Miss | н | Miss | Miss | Miss |

|--------------------|--------------------|------|------|------|---|------|------|------|

|--------------------|--------------------|------|------|------|---|------|------|------|

#### *P*-2-1-1-17 (34 accesses, 191ns)

Miss (intended) (intended) Hiss Hearbard Miss Hearbard Miss Hearbard Miss Hearbard Miss Hearbard Miss Hearbard Miss

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss<br>(intended) | Miss<br>(intended) | Miss | Miss | Miss | н | Miss | Miss | Miss |

|--------------------|--------------------|------|------|------|---|------|------|------|

|--------------------|--------------------|------|------|------|---|------|------|------|

#### *P*-2-1-1-17 (34 accesses, 191ns)

Mas (interded) which whi

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss<br>(intended) | Miss<br>(intended) | Miss | Miss | Miss | н | Miss | Miss | Miss |

|--------------------|--------------------|------|------|------|---|------|------|------|

|--------------------|--------------------|------|------|------|---|------|------|------|

#### *P*-2-1-1-17 (34 accesses, 191ns)

Miss (intended) webshelpeline Miss Miss Miss Miss Miss Miss Miss

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss<br>(intended) | Miss<br>(intended) | H Miss | Miss | Miss | H Mi | ss Miss | Miss | н |

|--------------------|--------------------|--------|------|------|------|---------|------|---|

|--------------------|--------------------|--------|------|------|------|---------|------|---|

#### *P*-2-1-1-17 (34 accesses, 191ns)

Mas (intended) Fiberbehreber Mas Heberbehreber Mas Heberbehreber Mas Heberbehreber

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss Miss<br>(intended) (intended) | H Miss | Miss | Miss | H Miss | Miss | Miss | H Miss |

|------------------------------------|--------|------|------|--------|------|------|--------|

|------------------------------------|--------|------|------|--------|------|------|--------|

#### *P*-2-1-1-17 (34 accesses, 191ns)

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss Mi<br>(intended) (inter | liss<br>nded) | Miss | Miss | Miss | H Miss | Miss | Miss | H Miss | Miss |

|------------------------------|---------------|------|------|------|--------|------|------|--------|------|

|------------------------------|---------------|------|------|------|--------|------|------|--------|------|

#### *P*-2-1-1-17 (34 accesses, 191ns)

Miss (intended) webshelpeline Miss Miss Miss Miss Miss Miss Miss

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss<br>(intended) | Miss<br>(intended) | H Miss | Miss | Miss | H Miss | Miss | Miss | H Miss | Miss | Miss |  |

|--------------------|--------------------|--------|------|------|--------|------|------|--------|------|------|--|

|--------------------|--------------------|--------|------|------|--------|------|------|--------|------|------|--|

#### *P*-2-1-1-17 (34 accesses, 191ns)

Mas (intended) Poleteleteret Mas Poleteleteret Mas viewerter Mas

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss<br>(intended) | Miss<br>(intended) | H Miss | Miss | Miss | H Miss | Miss | Miss | H Miss | Miss | Miss | н |

|--------------------|--------------------|--------|------|------|--------|------|------|--------|------|------|---|

|--------------------|--------------------|--------|------|------|--------|------|------|--------|------|------|---|

#### *P*-2-1-1-17 (34 accesses, 191ns)

Miss (intended) whether Miss interference Miss i

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss<br>(intended) | Miss<br>(intended) | Miss | Miss | Miss | H Miss | Miss | Miss | H Miss | Miss | Miss | H Miss |

|--------------------|--------------------|------|------|------|--------|------|------|--------|------|------|--------|

|--------------------|--------------------|------|------|------|--------|------|------|--------|------|------|--------|

#### *P*-2-1-1-17 (34 accesses, 191ns)

Mas (intended) Poleteleteret Mas Poleteleteret Mas viewerter Mas

#### P-1-1-1-17 (17 accesses, 307ns)

| Miss<br>(intended) | Miss<br>(intended) | H Miss | Miss | Miss | Miss | Miss | Miss | H Miss | Miss | Miss | H Miss | Miss |

|--------------------|--------------------|--------|------|------|------|------|------|--------|------|------|--------|------|

|--------------------|--------------------|--------|------|------|------|------|------|--------|------|------|--------|------|

#### *P*-2-1-1-17 (34 accesses, 191ns)

Mas (intended) Poleteleteret Mas Poleteleteret Mas viewerter Mas

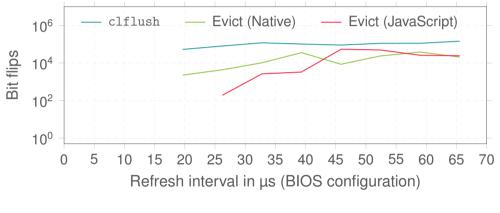

### Evaluation on Haswell

Figure: Number of bit flips within 15 minutes.

# Rowhammer.js: Take-Away

- cache eviction fast enough to replace clflush

- independent of programming language and available instructions

- first remote fault attack, from a browser

E. Bosman, K. Razavi, H. Bos, and C. Giuffrida. "Dedup Est Machina: Memory Deduplication as an Advanced Exploitation Vector". In: S&P'16. 2016.

# Rowhammer.js: Take-Away

- cache eviction fast enough to replace clflush

- independent of programming language and available instructions

- first remote fault attack, from a browser

- if you think a fault is not exploitable, think again

E. Bosman, K. Razavi, H. Bos, and C. Giuffrida. "Dedup Est Machina: Memory Deduplication as an Advanced Exploitation Vector". In: S&P'16. 2016.

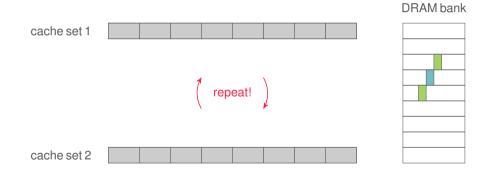

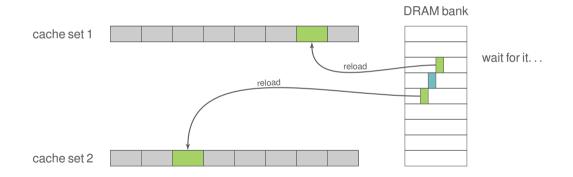

### DRAMA: Motivation (1)

a lot of wasted time

### DRAMA: Motivation (1)

a lot of wasted time

or a side channel?

# DRAMA: Motivation (2)

- cache attacks: either not across CPUs, or need shared memory

- limits attacks in restrictive environments

P. Pessl, D. Gruss, C. Maurice, M. Schwarz, and S. Mangard. "DRAMA: Exploiting DRAM Addressing for Cross-CPU Attacks". In: USENIX Security Symposium. 2016.

# DRAMA: Motivation (2)

- cache attacks: either not across CPUs, or need shared memory

- limits attacks in restrictive environments

- $\rightarrow\,$  exploiting the DRAM, across CPUs and without shared memory

P. Pessl, D. Gruss, C. Maurice, M. Schwarz, and S. Mangard. "DRAMA: Exploiting DRAM Addressing for Cross-CPU Attacks". In: USENIX Security Symposium. 2016.

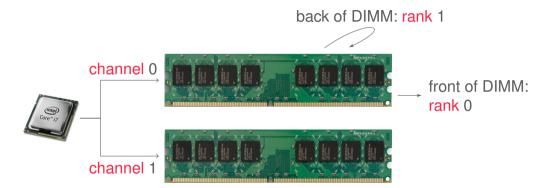

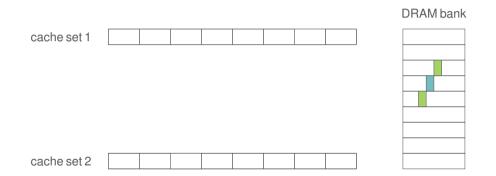

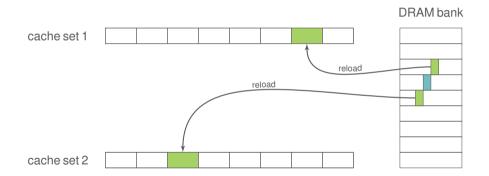

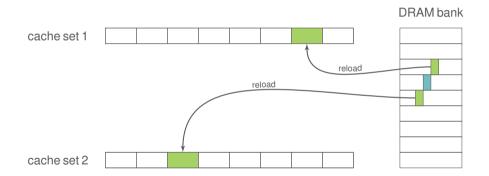

# DRAM organization example

- bits in cells in rows

- access: activate row, copy to row buffer

- row buffer  $\rightarrow$  cache!

# DRAM organization example

- bits in cells in rows

- access: activate row, copy to row buffer

- row buffer  $\rightarrow$  cache!

- $\rightarrow\,$  how to exploit these caches?

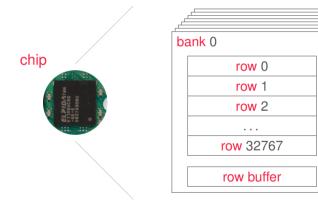

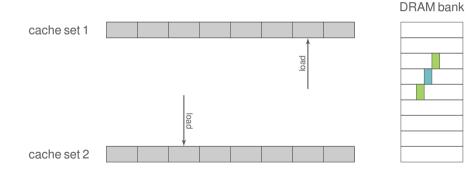

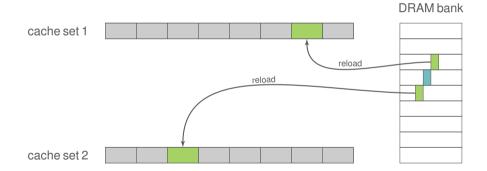

# Row hit and row conflict

When accessing a row i in a bank:

- row hit: row *i* already opened in row buffer  $\rightarrow$  fast

- row conflict: row  $j \neq i$  opened in the same bank  $\rightarrow$  slow

# DRAM timing differences

Cache hit

Cache miss, row hit

Cache miss, row conflict

### Example attack

- side-channel: template attack

- allocate a large fraction of memory to be in a row with the victim

- profile memory and record row-hit ratio for each address

### Take-away

- performance optimizations  $\rightarrow$  side channels

- $\hfill caches \rightarrow \hfill leakage$

- today's computers are fast because: lots of small optimizations

- ightarrow computers won't stop leaking

# Microarchitectural Incontinence You would leak too if you were so fast!

Daniel Gruss Graz University of Technology

October 18, 2016 — Hacktivity

# References I

- [BRBG16]

E. Bosman, K. Razavi, H. Bos, and C. Giuffrida. "Dedup Est Machina: Memory Deduplication as an Advanced Exploitation Vector". In: S&P'16. 2016.

- [GBM15] D. Gruss, D. Bidner, and S. Mangard. "Practical Memory Deduplication Attacks in Sandboxed Javascript". In: ESORICS'15. 2015.

- [GIES15] B. Gülmezoğlu, M. S. Inci, T. Eisenbarth, and B. Sunar. "A Faster and More Realistic Flush+Reload Attack on AES". In: COSADE'15. 2015.

- [GMM16] D. Gruss, C. Maurice, and S. Mangard. "Rowhammer.js: A Remote Software-Induced Fault Attack in JavaScript". In: DIMVA'16. 2016.

- [GMWM16] D. Gruss, C. Maurice, K. Wagner, and S. Mangard. "Flush+Flush: A Fast and Stealthy Cache Attack". In: DIMVA'16. 2016.

- [GSM15] D. Gruss, R. Spreitzer, and S. Mangard. "Cache Template Attacks: Automating Attacks on Inclusive Last-Level Caches". In: USENIX Security Symposium. 2015.

# References II

- [KPK14] V. P. Kemerlis, M. Polychronakis, and A. D. Keromytis. "ret2dir: Rethinking kernel isolation". In: USENIX Security Symposium. 2014, pp. 957–972.

- [LGSMM16] M. Lipp, D. Gruss, R. Spreitzer, C. Maurice, and S. Mangard. "ARMageddon: Last-Level Cache Attacks on Mobile Devices". In: USENIX Security Symposium. 2016.

- [LYGHL15] F. Liu, Y. Yarom, Q. Ge, G. Heiser, and R. B. Lee. "Last-Level Cache Side-Channel Attacks are Practical". In: S&P'15. 2015.

- [MLSNHF15] C. Maurice, N. Le Scouarnec, C. Neumann, O. Heen, and A. Francillon. "Reverse Engineering Intel Complex Addressing Using Performance Counters". In: RAID. 2015.

- [OKSK15] Y. Oren, V. P. Kemerlis, S. Sethumadhavan, and A. D. Keromytis. "The Spy in the Sandbox: Practical Cache Attacks in JavaScript and their Implications". In: CCS'15. 2015.

- [PGMSM16] P. Pessl, D. Gruss, C. Maurice, M. Schwarz, and S. Mangard. "DRAMA: Exploiting DRAM Addressing for Cross-CPU Attacks". In: USENIX Security Symposium. 2016.

# References III

[Sea15] M. Seaborn. How physical addresses map to rows and banks in DRAM. http://lackingrhoticity.blogspot.com/2015/05/how-physical-addressesmap-to-rows-and-banks.html. Retrieved on July 20, 2015. 2015.

[YF14] Y. Yarom and K. Falkner. "Flush+Reload: a High Resolution, Low Noise, L3 Cache Side-Channel Attack". In: USENIX Security Symposium. 2014.

### Granularity of the attacks

- 8 out of 64 regions (= 512 B) map to the same bank.

- each row is divided among 16 different pages (A – P)

- occupying 1 page B to P enough to spy on the eight 64-byte regions of page A in the same bank

- $\rightarrow$  granularity: 512 B = 2 cache lines