## Software-based Microarchitectural Attacks

## **Daniel Gruss**

April 19, 2018

Graz University of Technology

- Daniel Gruss

- Post-Doc @ Graz University of Technology

- Twitter: @lavados

- Email: daniel.gruss@iaik.tugraz.at

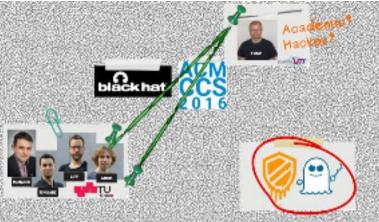

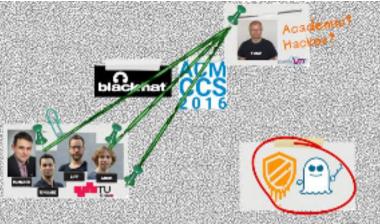

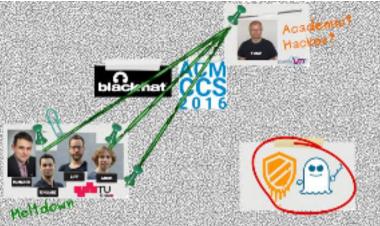

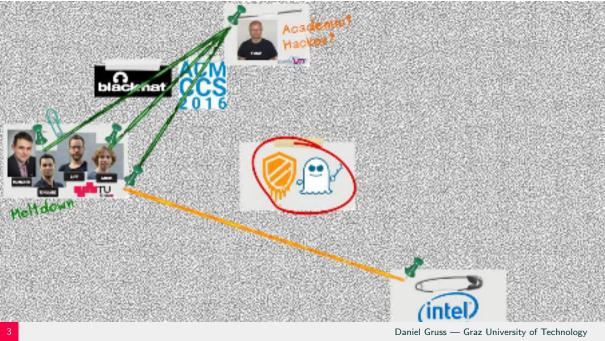

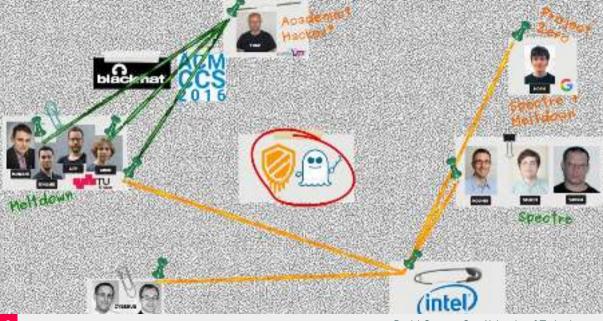

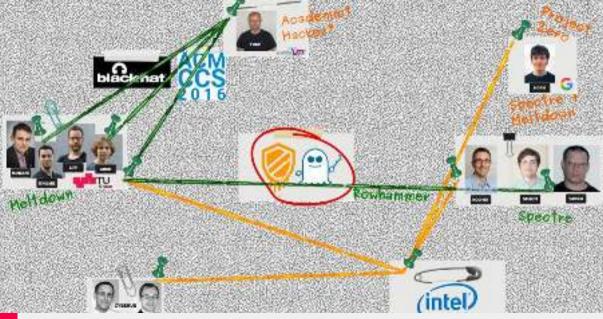

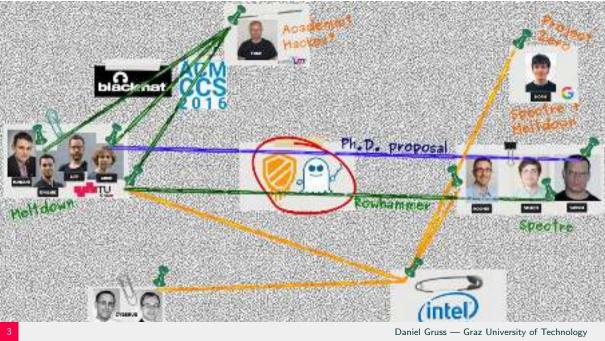

• Both vulnerabilities existed for many years

- Both vulnerabilities existed for many years

- No one discovered it before

- Both vulnerabilities existed for many years

- No one discovered it before

- Suddenly, 4 independent teams discover it within 6 months

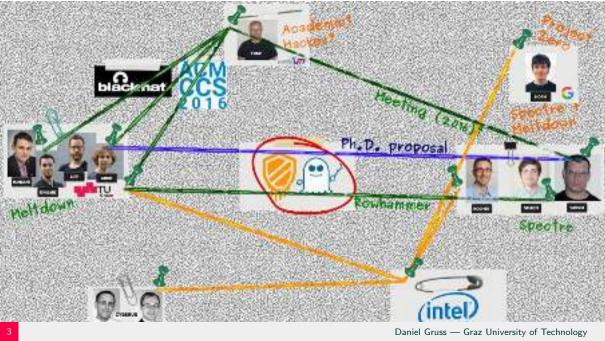

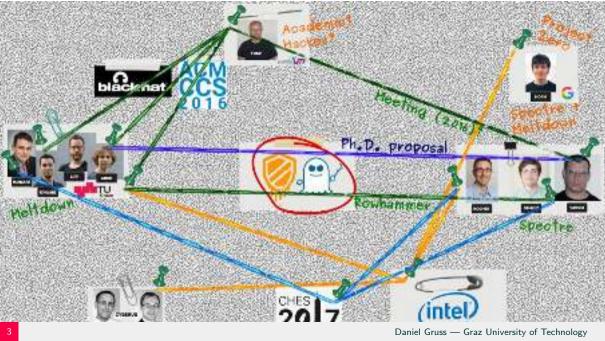

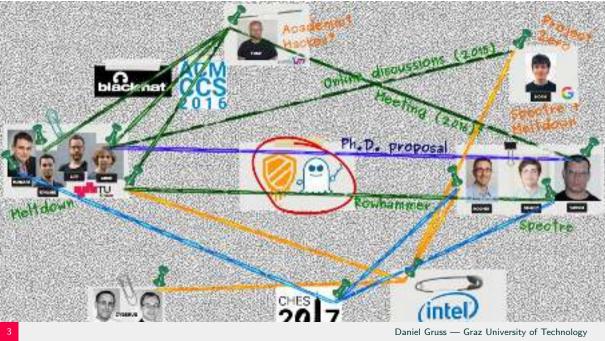

- Both vulnerabilities existed for many years

- No one discovered it before

- Suddenly, 4 independent teams discover it within 6 months

- Let's create an evidence board

Daniel Gruss — Graz University of Technology

Daniel Gruss — Graz University of Technology

• Two different problems

- Two different problems

- They only have a very loose connection

- Two different problems

- They only have a very loose connection

- Two different teams had already quite matured drafts ready when learning of each other

- Two different problems

- They only have a very loose connection

- Two different teams had already quite matured drafts ready when learning of each other

- Initially we tried to merge, but all co-authors quickly agreed that it would mix things that don't belong together

- $\rightarrow$  More on that after we understand the attacks

The Fallout

You realize it is something big when...

The Fallout

You realize it is something big when...

• it is in the news, all over the world

The Fallout www.tugraz.at

You realize it is something big when...

- it is in the news, all over the world

- you get a Wikipedia article in multiple languages

b

Officed Streets Section Formated Changest Editional Fire

About 65th with

Contenually body

Record charges

Contract coupe

**Shorts**

Melations was leased a Common Webstatilities and Exposures ID of DVE-2017. IDS44, also known as Mague Data Cache Cood. If is January 2016. It was disclosed to conjunction with another english, Spectre, with which it abuses some, but not all characteristics. The Melations and Spectre extrembilities are considered "categorists".

naturating equipment. A purely software workground to Mottlews has been assessed.

as allowing connectors between 5 and 30 servers to certain specialized workloads (\*\*)

alfeauth corespond respondite for software correction of the exploit are reporting

minimal impact from general benchmark testing 25

vairanabley

## WIKIPEDIA The Proc Spirvelopedia.

Man page Cotteros Parateonal comment Clumping coverage **Gasclery whole** Districts to Whitesta Millional to street

Interactions

Alexan Williamson Community ponisi Ricard charges Contact page

Soots

lifted total base Related strangers

Free Welparks the heat attractionality

Species is a visit enablity that offects mustern managing enable that perform branch prediction, FEED On most processors, the speculative execution resulting from a branch exprediction may leave observable side effects that may reveal private data to attackers. For example, if the cultern of reamony accesses performed by such speculative execution depends on private data, the resulting state of the data cautie constitutes a sink channel through which an attacker may be able to extract information selected that provide state contact a foreign attack 1453(6).

Two Continue, Vulneyabilities and Exposumes (De related to Specific, CVE-2517-67556) (bounds shock byzasa) and CVE-2017-8715W (moreth target transfort), have been based Fig. IIT engines used for JavaScript were toured valuestie. A website up touch data stored in the trougher for another website, or the because's memory build [1]

Several procedures to help protect home consulters and related devices from the Spectra land Motificens occurris variantabilities have been published PRESCHUSS Spectra patrities have been reported to significantly store down performance, especially on older computers; on the never 8th generation Core platforms, benchmark performance drops of 2-14 percent have been measured.<sup>112</sup> Melidown painties may also produce performance loss INSMERT On January 18, 2018, prepared retoods, even for never intel shops, size to

The Fallout www.tugraz.at

You realize it is something big when...

- it is in the news, all over the world

- you get a Wikipedia article in multiple languages

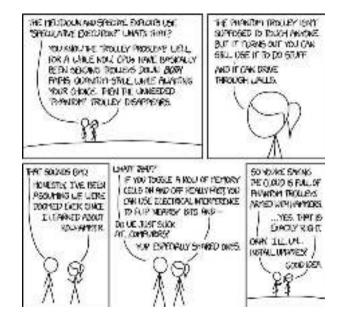

- there are comics, including xkcd

The Fallout www.tugraz.at

You realize it is something big when...

- it is in the news, all over the world

- you get a Wikipedia article in multiple languages

- there are comics, including xkcd

- you get a lot of Twitter follower after Snowden mentioned you

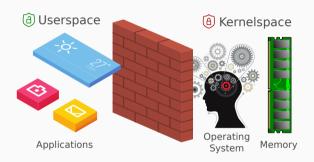

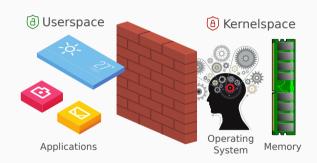

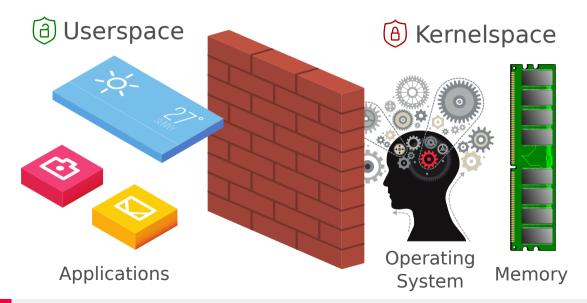

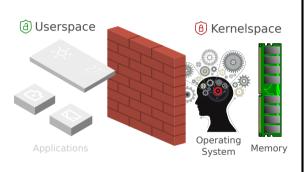

The Wall

• Kernel is isolated from user space

- Kernel is isolated from user space

- This isolation is a combination of hardware and software

- Kernel is isolated from user space

- This isolation is a combination of hardware and software

- User applications cannot access anything from the kernel

- Kernel is isolated from user space

- This isolation is a combination of hardware and software

- User applications cannot access anything from the kernel

- There is only a well-defined interface → syscalls

Daniel Gruss — Graz University of Technology

Daniel Gruss — Graz University of Technology

Daniel Gruss — Graz University of Technology

## 1337 4242

## **FOOD CACHE**

**Revolutionary** concept!

Store your food at home, never go to the grocery store during cooking.

Can store ALL kinds of food.

ONLY TODAY INSTEAD OF \$1,300

\$1,299

ORDER VIA PHONE: +555 12345

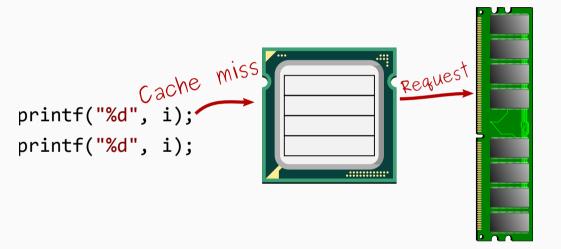

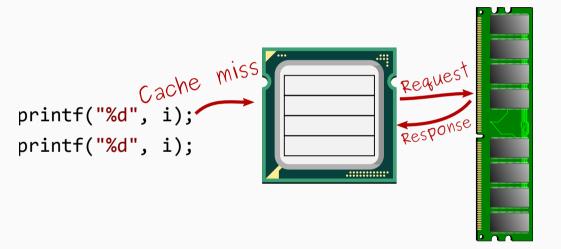

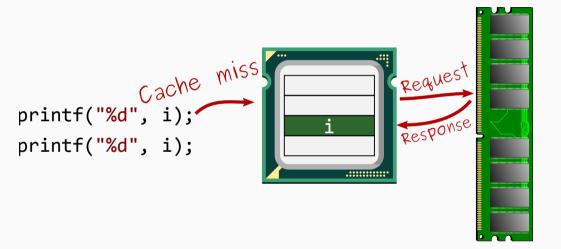

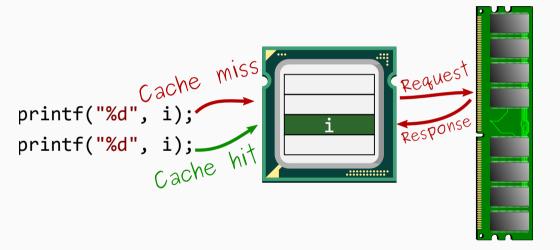

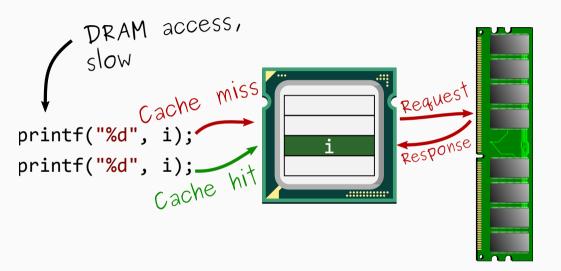

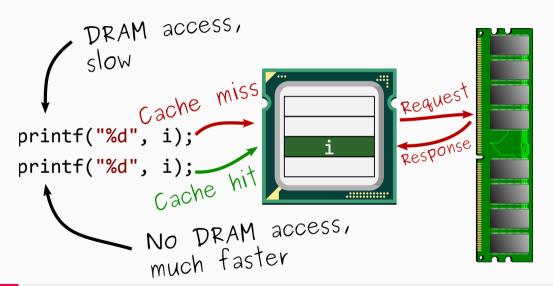

```

printf("%d", i);

printf("%d", i);

```

```

printf("%d", i);

printf("%d", i);

```

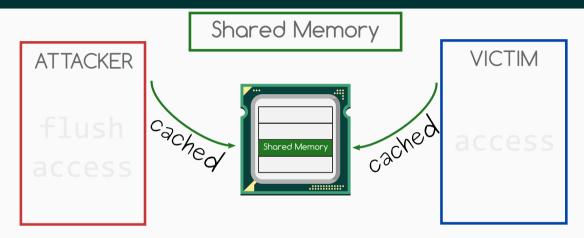

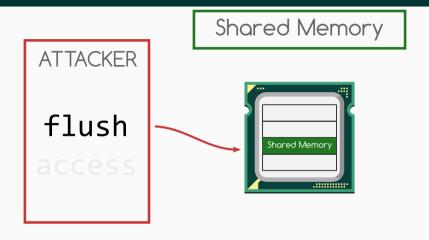

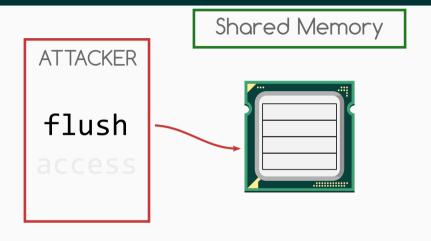

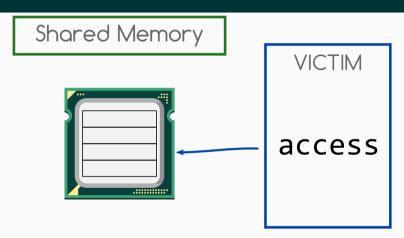

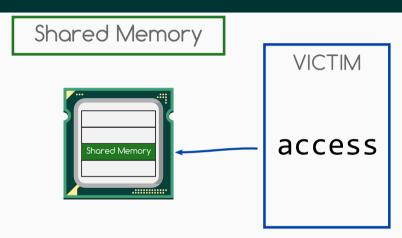

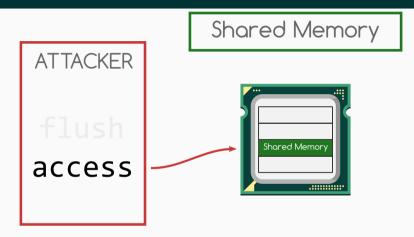

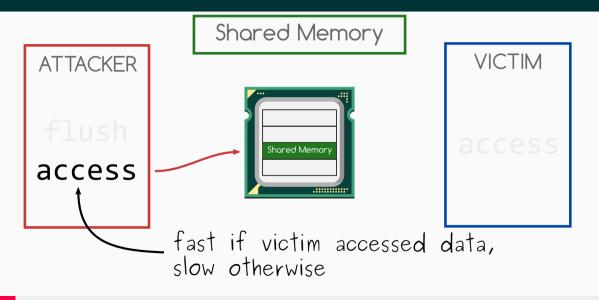

ATTACKER

Shared Memory

VICTIM

www.tugraz.at

www.tugraz.at

# Wait for an hour

# Wait for an hour

# LATENCY

- 1. Wash and cut vegetables

- Pick the basil leaves and set aside

- 3. Heat 2 tablespoons of oil in a pan

- 4. Fry vegetables until golden and softened

- 1. Wash and cut vegetables

- 2. Pick the basil leaves and set aside

- 3. Heat 2 tablespoons of oil in a pan

- 4. Fry vegetables until golden and softened

# Dependency

#### Parallelize

```

segfault at fffffffff81a000e0 ip 00000000000400535 sp 00007ffce4a80610 error 5 in reader

```

```

segfault at fffffffff81a000e0 ip 0000000000400535

sp 00007ffce4a80610 error 5 in reader

```

• Kernel addresses are not accessible

```

segfault at fffffffff81a000e0 ip 0000000000400535

sp 00007ffce4a80610 error 5 in reader

```

- Kernel addresses are not accessible

- Are privilege checks also done when executing instructions out of order?

```

*(volatile char*)0;

array[84 * 4096] = 0; // unreachable

```

• Adapted code

```

*(volatile char*)0;

array[84 * 4096] = 0; // unreachable

```

• Static code analyzer is not happy

```

warning: Dereference of null pointer *(volatile char*)0;

```

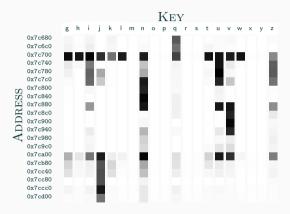

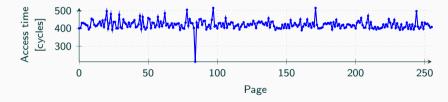

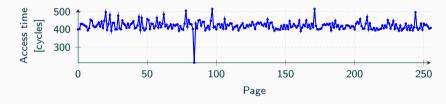

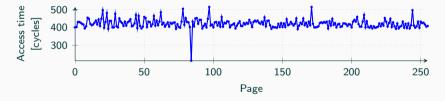

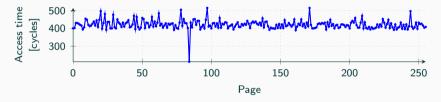

• Flush+Reload over all pages of the array

• "Unreachable" code line was actually executed

• Flush+Reload over all pages of the array

- "Unreachable" code line was actually executed

- Exception was only thrown afterwards

• Combine the two things

• Combine the two things

- = sending end of a cache covert channel

- Then check whether any part of array is cached

• Combine the two things

- = sending end of a cache covert channel

- Then check whether any part of array is cached

- = receiving end of a cache covert channel

• Flush+Reload over all pages of the array

• Index of cache hit reveals data

• Flush+Reload over all pages of the array

- Index of cache hit reveals data

- Permission check is in some cases not fast enough

| nīlov   | ck Pas | CHOMPSO  | el Ma  | nane  | e:  |        |    |

|---------|--------|----------|--------|-------|-----|--------|----|

| history | MICHA  | eletion. | 1/2    | - The |     |        |    |

|         |        |          | Untack |       |     | 971    |    |

|         |        |          |        |       | - 4 | Unince | 90 |

×

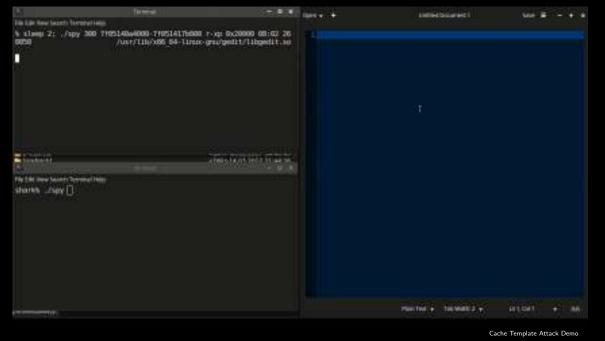

```

meltdown@meltdown -/ppm2 % taskset 1 ./imgdump 0x375a00000 14919 > outp

ut.flif

Reading from 0xffff880375a00000

```

### AND IN OTHER NEWS...

WE'RE ALL DOOMED, SANDRA.

HOW ABOUT THE WEATHER?

Not so fast...

• Kernel addresses in user space are a problem

Take the kernel addresses...

- Kernel addresses in user space are a problem

- Why don't we take the kernel addresses...

Daniel Gruss — Graz University of Technology

...and remove them

• ...and remove them if not needed?

...and remove them

- ...and remove them if not needed?

- User accessible check in hardware is not reliable

• Let's just unmap the kernel in user space

- Let's just unmap the kernel in user space

- Kernel addresses are then no longer present

- Let's just unmap the kernel in user space

- Kernel addresses are then no longer present

- Memory which is not mapped cannot be accessed at all

Kernel Address Isolation to have Side channels Efficiently Removed

#### KAISER /'knizə/

- 1. [german] Emperor, ruler of an empire

- 2. largest penguin, emperor penguin

Kernel Address Isolation to have Side channels Efficiently

#### **Kernel View**

#### **User View**

• We published KAISER in July 2017

- We published KAISER in July 2017

- Intel and others improved and merged it into Linux as KPTI (Kernel Page Table Isolation)

- We published KAISER in July 2017

- Intel and others improved and merged it into Linux as KPTI (Kernel Page Table Isolation)

- Microsoft implemented similar concept in Windows 10

- We published KAISER in July 2017

- Intel and others improved and merged it into Linux as KPTI (Kernel Page Table Isolation)

- Microsoft implemented similar concept in Windows 10

- Apple implemented it in macOS 10.13.2 and called it "Double Map"

- We published KAISER in July 2017

- Intel and others improved and merged it into Linux as KPTI (Kernel Page Table Isolation)

- Microsoft implemented similar concept in Windows 10

- Apple implemented it in macOS 10.13.2 and called it "Double Map"

- All share the same idea: switching address spaces on context switch

• Depends on how often you need to switch between kernel and user space

- Depends on how often you need to switch between kernel and user space

- Can be slow, 40% or more on old hardware

- Depends on how often you need to switch between kernel and user space

- Can be slow, 40% or more on old hardware

- But modern CPUs have additional features

- Depends on how often you need to switch between kernel and user space

- Can be slow, 40% or more on old hardware

- But modern CPUs have additional features

- ⇒ Performance overhead on average below 2%

# **SPECTRE**

# **SPECTRE**

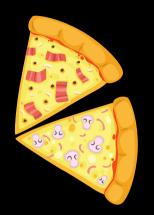

# **Prosciutto**

# Funghi

# **Speculative Cooking**

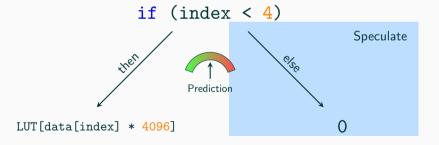

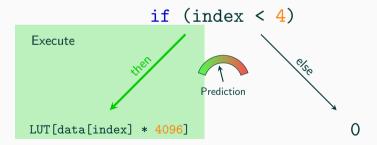

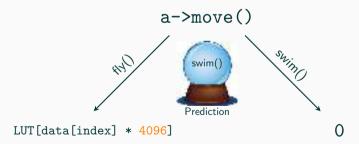

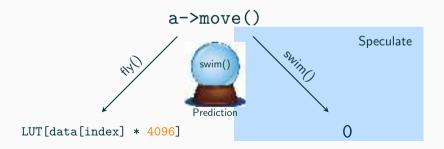

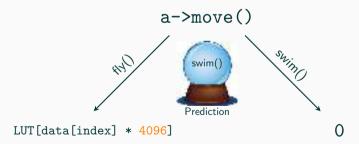

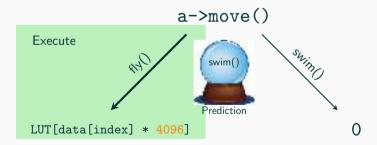

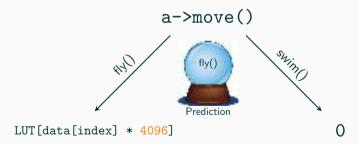

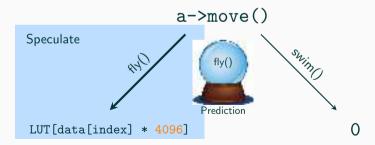

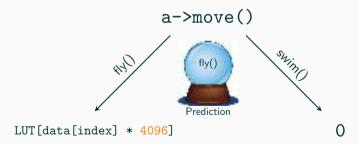

• Mistrains branch prediction

- Mistrains branch prediction

- CPU speculatively executes code which should not be executed

- Mistrains branch prediction

- CPU speculatively executes code which should not be executed

- Can also mistrain indirect calls

- Mistrains branch prediction

- CPU speculatively executes code which should not be executed

- Can also mistrain indirect calls

- → Spectre "convinces" program to execute code

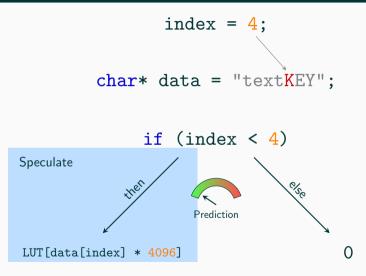

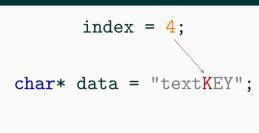

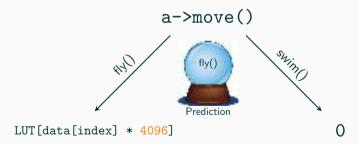

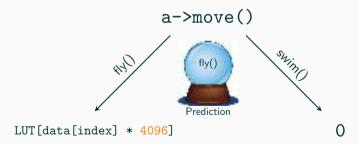

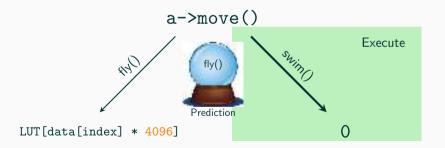

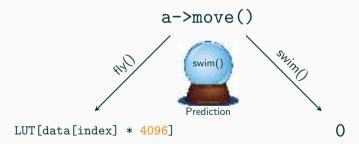

LUT[data[index] \* 4096]

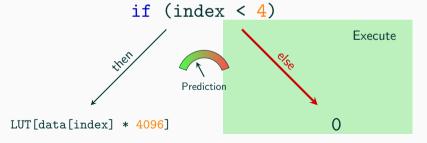

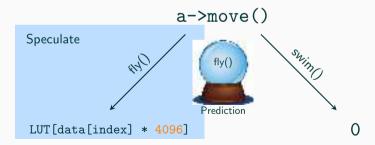

```

index = 1;

char* data = "textKEY";

if (index < 4)

Speculate

Prediction

LUT[data[index] * 4096]

```

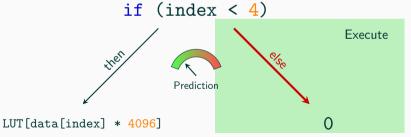

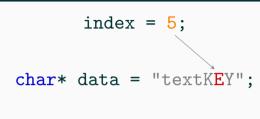

```

index = 2;

char* data = "textKEY";

if (index < 4)

Speculate

Prediction

LUT[data[index] * 4096]

```

• Trivial approach: disable speculative execution

- Trivial approach: disable speculative execution

- No wrong speculation if there is no speculation

- Trivial approach: disable speculative execution

- No wrong speculation if there is no speculation

- Problem: massive performance hit!

- Trivial approach: disable speculative execution

- No wrong speculation if there is no speculation

- Problem: massive performance hit!

- Also: How to disable it?

- Trivial approach: disable speculative execution

- No wrong speculation if there is no speculation

- Problem: massive performance hit!

- Also: How to disable it?

- Speculative execution is deeply integrated into CPU

• Workaround: insert instructions stopping speculation

- Workaround: insert instructions stopping speculation

- $\rightarrow\,$  insert after every bounds check

- Workaround: insert instructions stopping speculation

- $\rightarrow\,$  insert after every bounds check

- ×86: LFENCE, ARM: CSDB

- Workaround: insert instructions stopping speculation

- $\rightarrow\,$  insert after every bounds check

- x86: LFENCE, ARM: CSDB

- Available on all Intel CPUs, retrofitted to existing ARMv7 and ARMv8

• Speculation barrier requires compiler supported

- Speculation barrier requires compiler supported

- Already implemented in GCC, LLVM, and MSVC

- Speculation barrier requires compiler supported

- Already implemented in GCC, LLVM, and MSVC

- $\bullet$  Can be automated (MSVC)  $\to$  not really reliable

- Speculation barrier requires compiler supported

- Already implemented in GCC, LLVM, and MSVC

- ullet Can be automated (MSVC) o not really reliable

- Explicit use by programmer: \_\_builtin\_load\_no\_speculate

```

// Unarotected

ur. errey[4]:

int get_value(unsigned int h) {

int the:

证 (国来等) {

tmp - array[1]

} else {

return that

```

```

// Unarctected

una er nev[4]:

int cet value(unstoned int n) {

int the:

证 (国来等) {

tmp - array[n]

} else !

return that

```

```

// Protected

int array[X];

int get_value(unsigned int n) {

int *lower - array:

int Aptr = array + n;

int rupper - array + N;

return

(otr. lower, upper, FAIL):

```

Speculation barrier works if affected code constructs are known

- Speculation barrier works if affected code constructs are known

- Programmer has to fully understand vulnerability

- Speculation barrier works if affected code constructs are known

- Programmer has to fully understand vulnerability

- Automatic detection is not reliable

- Speculation barrier works if affected code constructs are known

- Programmer has to fully understand vulnerability

- Automatic detection is not reliable

- Non-negligible performance overhead of barriers

0-1-0-1-0 1-0-1-0-1 0-1-0-1-0 1-0-1-0-1 Intel released microcode updates

• Indirect Branch Restricted Speculation (IBRS):

01-01-0 1-0-1-0 1-0-1-0 1-0-1-0-1

- Indirect Branch Restricted Speculation (IBRS):

- Do not speculate based on anything before entering IBRS mode

01-01-0 1-01-01 01-01-0 1-01-01

- Indirect Branch Restricted Speculation (IBRS):

- Do not speculate based on anything before entering IBRS mode

- $\rightarrow\,$  lesser privileged code cannot influence predictions

61-61-6 1-61-61 61-61-61

- Indirect Branch Restricted Speculation (IBRS):

- Do not speculate based on anything before entering IBRS mode

- ightarrow lesser privileged code cannot influence predictions

- Indirect Branch Predictor Barrier (IBPB):

01-01-0 1-0-1-0 1-0-1-0-1

- Indirect Branch Restricted Speculation (IBRS):

- Do not speculate based on anything before entering IBRS mode

- ightarrow lesser privileged code cannot influence predictions

- Indirect Branch Predictor Barrier (IBPB):

- Flush branch-target buffer

01-01-0 1-01-01 01-01-01

- Indirect Branch Restricted Speculation (IBRS):

- Do not speculate based on anything before entering IBRS mode

- ightarrow lesser privileged code cannot influence predictions

- Indirect Branch Predictor Barrier (IBPB):

- Flush branch-target buffer

- Single Thread Indirect Branch Predictors (STIBP):

01-01-0 1-01-0-1 01-0-1-0 1-0-1-0-1

- Indirect Branch Restricted Speculation (IBRS):

- Do not speculate based on anything before entering IBRS mode

- ightarrow lesser privileged code cannot influence predictions

- Indirect Branch Predictor Barrier (IBPB):

- Flush branch-target buffer

- Single Thread Indirect Branch Predictors (STIBP):

- Isolates branch prediction state between two hyperthreads

# {...}

# Retpoline (compiler extension)

$\rightarrow$  always predict to enter an endless loop

- $\rightarrow$  always predict to enter an endless loop

- instead of the correct (or wrong) target function

- $\rightarrow$  always predict to enter an endless loop

- instead of the correct (or wrong) target function → performance?

- → always predict to enter an endless loop

- instead of the correct (or wrong) target function  $\rightarrow$  performance?

- On Broadwell or newer:

## Retpoline (compiler extension)

- → always predict to enter an endless loop

- instead of the correct (or wrong) target function  $\rightarrow$  performance?

- On Broadwell or newer:

- ret may fall-back to the BTB for prediction

## Retpoline (compiler extension)

- → always predict to enter an endless loop

- instead of the correct (or wrong) target function  $\rightarrow$  performance?

- On Broadwell or newer:

- ret may fall-back to the BTB for prediction

- $\rightarrow$  microcode patches to prevent that

• ARM provides hardened Linux kernel

- ARM provides hardened Linux kernel

- Clears branch-predictor state on context switch

- ARM provides hardened Linux kernel

- Clears branch-predictor state on context switch

- Either via instruction (BPIALL)...

- ARM provides hardened Linux kernel

- Clears branch-predictor state on context switch

- Either via instruction (BPIALL)...

- ...or workaround (disable/enable MMU)

- ARM provides hardened Linux kernel

- Clears branch-predictor state on context switch

- Either via instruction (BPIALL)...

- ...or workaround (disable/enable MMU)

- Non-negligible performance overhead ( $\approx 200\text{-}300\,\mathrm{ns}$ )

• Prevent access to high-resolution timer

- Prevent access to high-resolution timer

- $\,\,

ightarrow\,$  Own timer using timing thread

- Prevent access to high-resolution timer

- $\rightarrow\,$  Own timer using timing thread

- Flush instruction only privileged

- Prevent access to high-resolution timer

- $\rightarrow\,$  Own timer using timing thread

- Flush instruction only privileged

- → Cache eviction through memory accesses

- Prevent access to high-resolution timer

- $\rightarrow\,$  Own timer using timing thread

- Flush instruction only privileged

- ightarrow Cache eviction through memory accesses

- Just move secrets into secure world

- Prevent access to high-resolution timer

- ightarrow Own timer using timing thread

- Flush instruction only privileged

- ightarrow Cache eviction through memory accesses

- Just move secrets into secure world

- → Spectre works on secure enclaves

• Out-of-Order Execution

## Spectre

Speculative Execution (subset of Out-of-Order Execution)

- Out-of-Order Execution

- has nothing to do with branch prediction

- Speculative Execution (subset of Out-of-Order Execution)

- fundamentally builds on branch (mis)prediction

- Out-of-Order Execution

- has nothing to do with branch prediction

- turning off speculative execution entirely has no effect on Meltdown

- Speculative Execution (subset of Out-of-Order Execution)

- fundamentally builds on branch (mis)prediction

- turning off speculative execution entirely would work

- Out-of-Order Execution

- has nothing to do with branch prediction

- turning off speculative execution entirely has no effect on Meltdown

- → melts down the isolation provided by the user\_accessible-bit

- Speculative Execution (subset of Out-of-Order Execution)

- fundamentally builds on branch (mis)prediction

- turning off speculative execution entirely would work

- has nothing to do with the user\_accessible-bit

- Out-of-Order Execution

- has nothing to do with branch prediction

- turning off speculative execution entirely has no effect on Meltdown

- → melts down the isolation provided by the user\_accessible-bit

- in theory: OoO not required, pipelining can be sufficient

- Speculative Execution (subset of Out-of-Order Execution)

- fundamentally builds on branch (mis)prediction

- turning off speculative execution entirely would work

- has nothing to do with the user\_accessible-bit

- KAISER has no effect on Spectre at all

- Out-of-Order Execution

- has nothing to do with branch prediction

- turning off speculative execution entirely has no effect on Meltdown

- → melts down the isolation provided by the user\_accessible-bit

- in theory: OoO not required, pipelining can be sufficient

- mitigated by KAISER

- Speculative Execution (subset of Out-of-Order Execution)

- fundamentally builds on branch (mis)prediction

- turning off speculative execution entirely would work

- has nothing to do with the user\_accessible-bit

- KAISER has no effect on Spectre at all

ullet performs illegal memory accesses o we need to take care of processor exceptions

# Spectre

• performs only legal memory accesses

- performs illegal memory accesses → we need to take care of processor exceptions

- exception handling

- performs only legal memory accesses

- has nothing to do with exception handling

- ullet performs illegal memory accesses o we need to take care of processor exceptions

- exception handling

- exception suppression with TSX

- performs only legal memory accesses

- has nothing to do with exception handling or suppression

- performs illegal memory accesses → we need to take care of processor exceptions

- exception handling

- exception suppression with TSX

- exception suppression with branch misprediction

- performs only legal memory accesses

- has nothing to do with exception handling or suppression

- performs illegal memory accesses → we need to take care of processor exceptions

- exception handling

- exception suppression with TSX

- exception suppression with branch misprediction

# Spectre

- performs only legal memory accesses

- has nothing to do with exception handling or suppression

$\rightarrow$  two papers, two names, etc.

But ...

• "How can you use speculative execution maliciously?"

- "How can you use speculative execution maliciously?"

- Intel had much interest in not fancy-naming them;)

- "How can you use speculative execution maliciously?"

- Intel had much interest in not fancy-naming them;)

- "How can you use speculative execution maliciously?"

- Intel had much interest in not fancy-naming them ;)

- ... why were they presented on the same date and on the same website?

- "How can you use speculative execution maliciously?"

- Intel had much interest in not fancy-naming them ;)

- ... why were they presented on the same date and on the same website?

- We did not choose the date

- "How can you use speculative execution maliciously?"

- Intel had much interest in not fancy-naming them ;)

... why were they presented on the same date and on the same website?

- We did not choose the date

- We did not want to have one of them overshadow the other immediately

We have ignored microarchitectural attacks for many many years:

attacks on crypto

ullet attacks on crypto ightarrow "software should be fixed"

- $\bullet$  attacks on crypto  $\rightarrow$  "software should be fixed"

- attacks on ASLR

- $\bullet$  attacks on crypto  $\rightarrow$  "software should be fixed"

- $\bullet$  attacks on ASLR  $\rightarrow$  "ASLR is broken anyway"

- ullet attacks on crypto o "software should be fixed"

- $\bullet$  attacks on ASLR  $\rightarrow$  "ASLR is broken anyway"

- attacks on SGX and TrustZone

- $\bullet$  attacks on crypto  $\rightarrow$  "software should be fixed"

- ullet attacks on ASLR ightarrow "ASLR is broken anyway"

- ullet attacks on SGX and TrustZone o "not part of the threat model"

- $\bullet$  attacks on crypto  $\rightarrow$  "software should be fixed"

- ullet attacks on ASLR ightarrow "ASLR is broken anyway"

- attacks on SGX and TrustZone  $\rightarrow$  "not part of the threat model"

- ightarrow for years we solely optimized for performance

After learning about a side channel you realize:

After learning about a side channel you realize:

• the side channels were documented in the Intel manual

After learning about a side channel you realize:

- the side channels were documented in the Intel manual

- only now we understand the implications

Motor Vehicle Deaths in U.S. by Year

**Conclusions**

A unique chance to

rethink processor design

**Conclusions**

## A unique chance to

- rethink processor design

- grow up, like other fields (car industry, construction industry)

**Conclusions**

## A unique chance to

- rethink processor design

- grow up, like other fields (car industry, construction industry)

- dedicate more time into identifying problems and not solely in mitigating known problems

## Software-based Microarchitectural Attacks

## **Daniel Gruss**

April 19, 2018

Graz University of Technology